IBERT在FPGA中的應用

為確定高速串行接口的參數是否滿足硬件及多種環境的需求,可通過在對端器件高速串行接口設置遠端環回,設置待測試芯片的收發data pattern為統一模式,常溫及高低溫拷機,觀察誤碼率是否滿足要求,誤碼率需滿足E-10。例中與圖6對應的參數值條件下,對端器件高速串行接口設置遠端環回誤碼率為4.36E-10,滿足誤碼率要求。本文引用地址:http://cqxgywz.com/article/190002.htm

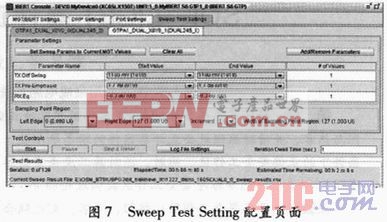

Sweep Test Setting(掃描測試)其配置頁面如圖7所示,以Rx Sampling Point來進行誤碼率測試定性分析信道質量為例,較為容易理解,當同定在某個采樣點進行誤碼測試時,誤碼率達到E-10時,可判定信道質量良好。在整個UI范圍內進行采樣點的掃描測試時,誤碼率達到E-10的采樣點越多,信號眼圖的眼睛張得越大,距離模板的余量越大,信道質量越好。

3 結束語

通過以上實例,可見IBERT具有可操作性較強的GUI圖形界面,可操作性強、準確、易用,可方便地設置高速串行收發通道的各項參數,并提供了多種環回模式及多種測試激勵源,并可通過自動掃描測試,確定收發的最佳參數。可以滿足硬件測試時對高速串行收發通道信號測試的大部分需求,在故障定位等場合均可使用。在單板的硬件測試初期,使用IBERT可以輔助硬件測試,例如設置發送通道的各項參數,協助示波器測量信號質量,而完全不需額外的開發FPGA邏輯。進行誤碼率測試,作為定量測量眼圖質量、jitter等指標的補充。從示波器看圖確定出的參數并非就是最佳參數。如示波器對于均衡后的信號質量無法測試,而通過IBERT測誤碼率能夠測試到均衡之后的節點,測試范圍更大。可以預見,集成比特誤碼測試儀IBERT將在FPGA設計中獲得廣泛應用。

評論