從StratixIII及CycloneIV開發板談FPGA配置

如圖,將撥碼開關撥至PROG端,就可以用PC對EPCS64配置芯片進行燒寫了。

1、先生成一個pof配置文件。在File下選擇Convert Programming File,這部分操作后面也會提到。

2、將撥碼開關撥至PROG,在Programmer中將模式選擇為AS mode,選擇pof文件。

3、Start,開始燒寫。這里可以發現,過程較sof文件的燒寫要漫長得多。

這里需要注意的是,其實上面圖中圈起部分是很容易引起誤解的。EPCS64要對FPGA進行配置時,撥碼開關仍然需要撥回到RUN端,可以理解成,只是換成了配置芯片把程序燒寫到FPGA中運行”罷了。

下面介紹另一種對EPCS64的配置方式,我們希望通過JTAG模式來對EPCS64進行配置。我們暫且稱它為jic文件模式。這里我們可以簡單把EPCS64當做一個Flash存儲器,既然是存儲器那肯定可以利用FPGA來對它進行寫入操作。這種模式下,就是通過JTAG對FPGA進行寫入操作,然后讓FPGA來對配置芯片進行寫入操作。

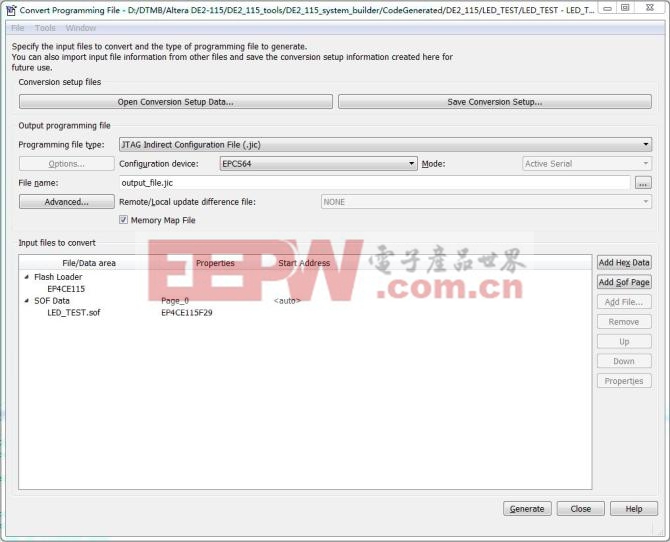

首先,還是通過Convert Programming File來生成一個jic文件。

我們可以看到在下面Input files to convert設置的時候,其中比之前的pof文件生成多了一個Flash Loader,也就是說,這里選的FPGA就是用來Loader配置芯片的。

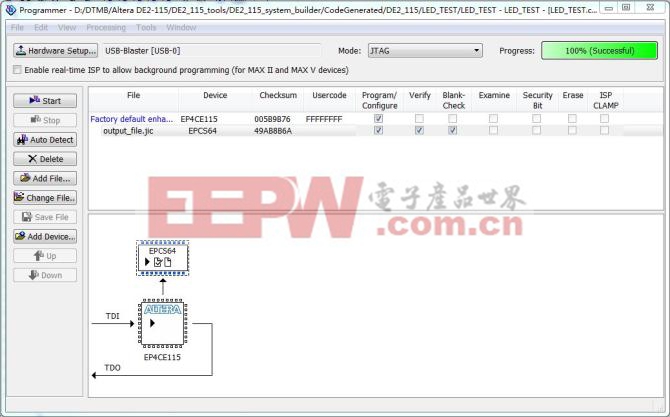

生成了jic文件后,在Programmer中選擇JTAG模式下載就行了,如下圖:

這里也有整個過程的體現,上圖的下面也顯示了整個燒寫過程的簡單示意圖。

評論