基于FPGA和FLASH ROM的圖像信號發生器設計

3 實驗結果與分析

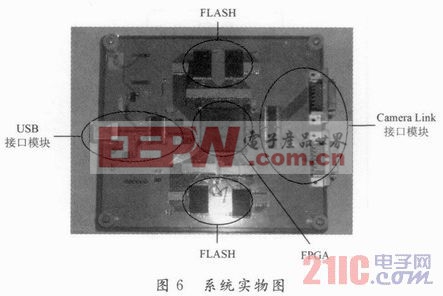

系統實物圖如圖6所示。本文引用地址:http://cqxgywz.com/article/190175.htm

為了檢測該信號發生器的性能,將其輸出接入圖像采集卡進行驗證。經過試驗驗證,FLASH ROM中存儲的圖像數據與從PC機載入的數據完全一致、控制時序符合設計要求。通過改變Strobe的頻率大小,驗證得到Camera Link輸出的像素時鐘頻率最大可以達到70 MHz。對于尺寸為128×128、位寬為8 b的目標圖像,在采用40 MHz的Strobe時鐘進行單通道輸出時,幀頻可以達到1 876 f/s。對于尺寸為512×512、位寬為8 b的目標圖像,當Strobe時鐘為70 MHz,單通道輸出時,幀頻可以達到252 f/s;雙通道輸出時,幀頻可以達到476 f/s。該信號發生器可以模擬目前大部分波前處理機所需的信號源。在進行單通道或雙通道輸出時,系統可以充分利用Camera Link接口的輸出能力。但是當進行更多通道的輸出時,由于受限于FLASH的讀出速率,該系統不能充分應用Camera Link接口的輸出能力。對于這個缺陷,在對系統進行改進時可以通過使用FLASH ROM和高速大容量RAM共同組成數據存儲模塊來解決。

4 結論

根據本文介紹的設計方案,采用FPGA技術設計的圖像信號發生器結構簡單,實現方便,易于修改。FLASH ROM提供了較高的數據讀出速率,支持系統能夠模擬出較高幀頻的CCD相機輸出。經過試驗驗證,系統工作穩定,達到了設計要求。

評論