基于單片機與FPGA可調延時模塊的設計

在P89C51RD2的64k閃存空間中,地址為0000H-7FFFH的32kB閃存空間作為程序空間,整個單片機程序編譯后為15k,所以32k的程序空間足夠大。余下的8000H?FFFFH的32kB 閃存空間留作數據存儲空間。兩塊數據存儲空間輪流使用,當數據量存滿其中一塊時通過程序跳轉到另一塊,在使用前先將該塊擦除。

各函數介紹如下:

main()——主程序;

InitUart(void)——串口初始化;

IapInit(void)——IAP功能初始化,使用IAP功能前必調用;

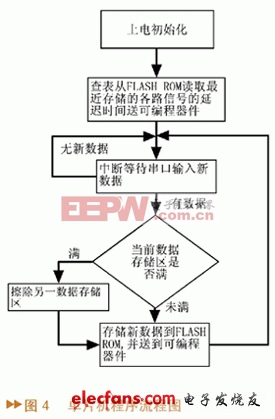

PowerOnRead(void)——上電讀取最近一次存儲的參數。模塊對上電時間要求不苛刻,最新數據的地址可通過查表方式尋找。每一個數據幀占一個數據存儲空間,由于單片機每次中斷都接收到8個數據幀,所以將每8個數據存儲空間劃分成一組,這樣只要查詢每組的頭一個地址就能快捷地完成查詢,大大節省了查詢時間。

EraseBlock (uint AddressRestore)——判斷當前數據存儲空間塊滿,并擦除;

RestoreData(void)——數據存儲在數據存儲空間;

FPGADataUp(uchar DataRec)——更新FPGA接口數據。

在程序中,要多次調用BootROM固件中的子程序。由于IAP子程序接口是匯編語言,為了編寫方便,同時使程序框架明了,編寫了一個IAPLIB.A51匯編語言接口函數庫和IAPLIB.H頭文件。在程序中加上IAP.H頭文件,調用固件程序時就不需在C51程序中嵌入匯編,而是像調用C語言函數一樣簡單,這大大簡化了編程。

FPGA設計

FPGA主要設計了DECODE延時通道譯碼器、CS片選信號控制器、N階SHIFTER移位寄存器。其中譯碼器用于完成對單片機并口送來的數據進行通道、時間參數的分離,用通道參數進行尋址和譯碼,這是一種簡單的譯碼邏輯和觸發電路。N階移位寄存器用于完成對信號進行N階的延時處理,是延時處理的核心單元。 延時通道譯碼器將單片機并口送來的延時參數送入鎖存器,同時輸出控制電路將移位寄存器對應的延時階切換到輸出端。從不同的階引出信號即可獲得不同的延時量。控制時鐘和移位寄存器的階數決定了延時步進調節精度和延時調節范圍。如果定時模塊有N個信號通道,每個定時模塊集成N個完全相同的延時調節單元,就可實現獨立調節各個通道信號延時大小的功能。集成的延時調節單元越多,占用可編程芯片的資源就越多,這可以根據實際需要選擇可編程邏輯器件。

FPAG軟件的設計采用“自頂向下”、“軟硬兼施”的設計方法,主要的各單元設計采用VHDL語言描述完成,而整個多路信號的延時功能處理采用圖形輸入設計方法。軟件設計完成后,根據電路原理圖進行引腳鎖定,然后啟動編譯程序來編譯項目。編譯器將進行錯誤檢查、網表提取、邏輯綜合和器件適配,然后進行行為仿真、功能仿真和時序仿真。最后通過編程器方式將POF文件下載到EPROM中。加電后,FPGA將EPROM中數據讀入片內編程RAM中,完成配置,從而生成硬件電路。

模塊功能調試實現

模塊在調試中出現P89C51RD2有時上電程序運行不正常,讀取程序空間是空的。但是只要上電工作起來,就恢復正常。懷疑由于上電復位時序混亂,造成誤調用固件擦除芯片子程序。采用專用復位芯片替換電容電阻加二極管的復位電路,使問題得到了解決。同樣,在單片機正確送數情況下,FPGA上電出現不能正常恢復預設好的延時信號,信號總是零延遲(第一次上電,單片機數據存儲空間內沒有數據,信號就處于零延時狀態),但在工作狀態下,能夠很好地實現延時調節。懷疑這種情況是因存在復位問題而導致,但專用復位芯片不能解決問題。經多次檢查程序,發現硬件語言程序中觸發語句是電平觸發,改寫為脈沖上升觸發后問題得以解決。

結束語

采用單片機和FPGA設計的延時調節模塊,硬件結構簡單,設計集成度高。軟件方面,單片機程序將C語言和匯編語言很好地結合,FPGA充分發揮了硬件語言易改變電路結構和算法的優越性。提高FPGA中移位寄存器的時鐘頻率,同時相應增加移位寄存器程序輸出階數,可實現更高精度的延時步進調節和增大延時調節范圍。因此可以在不改變模塊硬件結構基礎的上,通過軟件升級來提高模塊的性能,從而擴大模塊的應用領域。

評論