一種基于FPGA的UART 電路實現

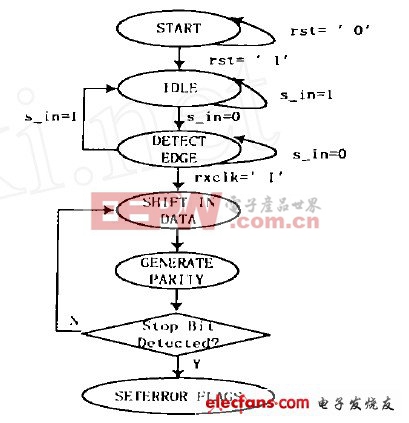

圖3 接收邏輯的流程

運用Modelsim 712 對接收模塊做了時序仿真,其結果如圖4 所示。接收時鐘與發(fā)送時鐘相同,接收到一幀串行數據,由接收模塊轉換為并行輸出,并且檢驗校驗位和停止位,產生fram ing_ erro r 和parity_ erro r 信號輸出。

圖4 接收模塊時序仿真波形圖

5 接口控制模塊

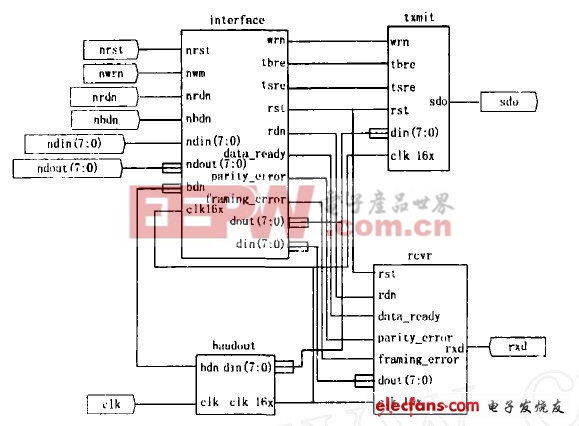

接口控制模塊連接控制發(fā)送、接收、波特率發(fā)生模塊,并與外部并行總線相連接,從外部(CPU 或單片機) 接收控制信號(nrst, nw rn, nbdn, nrdn) , 來控制UART 的發(fā)送、接收以及內部時鐘的生成。在nw rn 有效并且內部信號tbre= ′0′(發(fā)送緩沖寄存器空) 時,將數據總線輸入的并行數據發(fā)送給發(fā)送模塊數據線din (7: 0) , 執(zhí)行發(fā)送數據功能。在nrdn 有效并且內部信號data_ ready, parity_erro r, fram ing_ erro r 有效時,允許從接收模塊讀入接收到的數據。波特率發(fā)生器和發(fā)送模塊的并行數據輸入端口共用一個數據總線。

6 總體電路綜合及仿真

UART 總體電路如圖5 所示,分別由上述4 個模塊組成。其時序仿真如圖6 所示。

圖5 UART 總體電路圖

圖6 UART 總體時序仿真波形圖

觀察圖6, 可以看到串行輸出端口sdo 發(fā)送一幀數據為“00101011001”, 第一位為起始位,8 位數據位,校驗位為“0”(偶校驗) , 1 位停止位,空閑狀態(tài)位為高電平。并行輸出端口ndout 輸出為“00101010”, 輸入數據幀格式正確,校驗位正確。

7 結 語

用FPGA 器件實現了UART 異步收發(fā)器的核心功能,可以實現對數據的接收和發(fā)送,并可以在接收數據時對其校驗位、停止位進行判斷,在發(fā)送數據時可以形成完整的一幀數據格式。其接收和發(fā)送數據的時鐘有內部波特率發(fā)生器產生,根據預置的分頻系數,對外部時鐘進行分頻,產生需要的接收或發(fā)送時鐘。將該UART 電路作為一功能塊嵌入到一個FPGA 實現的數據采集與處理系統中,成功地實現了和遠端的PC 機進行異步串行通信。實驗證明該UART 電路簡單,工作穩(wěn)定、可靠,可運用于低端的異步通信。

評論