基于FPGA開發靜態無功補償控制器

用戶感言

“我們原來使用DSP開發板開發核心控制算法,再進行外圍硬件電路及外殼設計和封裝。現場運行的反饋是穩定性差,調試排錯困難,導致整個控制器的上市時間延長。在上海聚星儀器的協助下我們嘗試在NI CompactRIO平臺上開發控制算法,硬件接口邏輯設計,上下位機通信等功能,算法開發時間得到有效縮短,最終控制器發布并安裝到現場后系統穩定性大大提高。目前已銷售了多套在NI CompactRIO上實現控制器的靜態無功補償器。”

硬件:CompactRIO,cRIO 9012,cRIO 9114,NI 9205,NI 9215,NI 9401,NI 9403

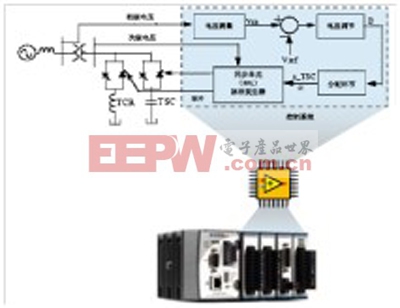

圖1 基于NI CompactRIO 的SVC全數字控制系統

圖2 LabVIEW編寫的PPL環節界面

評論