基于FPGA高階FIR濾波器的實現

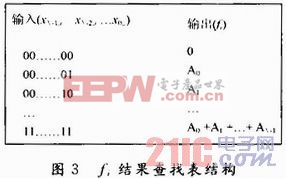

式中。ceil代表向上取整。存儲器的結構如圖3所示。

由圖3得到fi(i=0,1,2,…,N-1)的值,可直接進行后續的累加,在很大程度上節省累加器資源。由式(11)可知查找表的深度以2的冪指數增加,即濾波器的階數增加n位,則ROM深度增加2n倍,若濾波器的階數N很大,就會消耗很多的查找表資源。這種以2的冪指數遞增的資源消耗是硬件資源不可接受的。為了克服DA算法的缺點,提出了改進型DA算法結構。

2.2.2 改進型DA結構

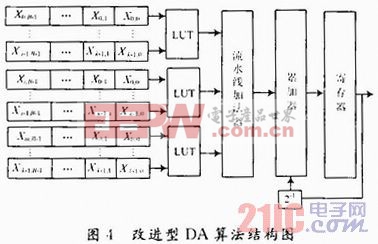

改進型DA結構是將濾波器系數平均放到多個存儲器中,每個存儲器形成一個LUT,然后將多個LUT的結果相加,并通過流水線寄存器來實現。圖4為改進型DA結構圖。

設濾波器的階數N=PQ,則fi可變形為式(13):

![]()

根據式(13),fi的實現只需要P個深度為2Q的查找表,在很大程度上減少了存儲器的地址空間,LUT的規模也隨地址空間的減小而呈現指數減小。

由于FPGA的查找表結構一般為4輸入,為了提高濾波器系統設計的效率,濾波器的階數N為4的整數倍。假設濾波器系數N取64,將64個系數按不同的組合相加作為查找表的數據,數據用16 b有符號數表示。采用DA結構,需要的存儲器地址空間為16×264b,顯然這樣規模的存儲單元消耗是系統無法承受的。而采用改進型DA結構,若存儲器的個數P=4,所需總的存儲器地址空間為16×4×216=416 Mb。若存儲器的個數P=8,所需總的存儲器地址空間為16×8×28=32 Mb。由此可見,采用改進型DA結構可使設計規模顯著減小,有效降低資源的消耗。

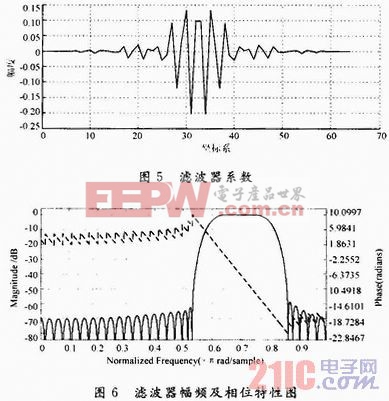

設濾波器為帶通濾波器,窗函數為凱賽窗(Kaiser),通帶截止頻率為0.65,0.75,阻帶起始頻率為0.55,0.85,通帶和阻帶的紋波系數為0.001,利用窗函數法設計,濾波器的階數為64階,其系數如圖5所示,幅頻及相頻特性如圖6所示。

評論