基于FPGA和DSP的1394b雙向數(shù)據(jù)傳輸系統(tǒng)

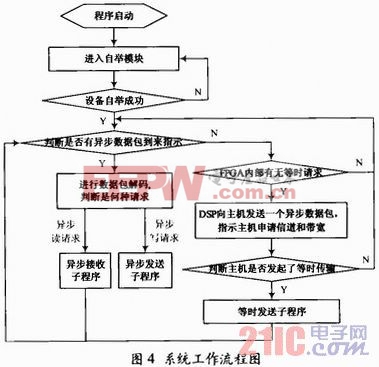

系統(tǒng)上電后,通常需要進行設備的自舉,協(xié)助主機完成設備識別和設備身份的確認,設備的自舉主要包括:初始化鏈路層寄存器;初始化配置ROM;判斷電纜是否插入;強制根節(jié)點;響應根節(jié)點、讀取配置ROM請求直到根節(jié)點調用相應驅動程序完成設備識別。圖4所示為本系統(tǒng)的工作流程圖。本文引用地址:http://cqxgywz.com/article/190437.htm

設備自舉完成以后,即可等待數(shù)據(jù)包的到來,根據(jù)數(shù)據(jù)包的類型,如果是異步數(shù)據(jù)包則進行相應的處理;如果是等時數(shù)據(jù)包則進行等時信道和帶寬的申請,申請成功后則配置DMA寄存器以DMA方式進行等時數(shù)據(jù)的發(fā)送或等時數(shù)據(jù)的接收,等時數(shù)據(jù)傳輸完畢后釋放其信道和帶寬,這樣完成一次數(shù)據(jù)的傳輸,接下來進行下一次數(shù)據(jù)的傳輸,如此循環(huán)完成整個數(shù)據(jù)的傳輸。

5 結束語

IEEE 1394b作為一種與平臺無關的技術,可以同時應用在MAC和PC中,本文研究的主要內容是利用FPGA、DSP和PCI9054芯片實現(xiàn)1394b數(shù)據(jù)傳輸系統(tǒng)。現(xiàn)在國內基本上還停留在1394或1394a總線數(shù)據(jù)的傳輸上,本系統(tǒng)是在前人的基礎上,實現(xiàn)1394b總線上的數(shù)據(jù)傳輸,同時本系統(tǒng)兼容1394a實現(xiàn)1394的傳輸,還可以將傳輸速率提高作為驗證1394b協(xié)議的通用平臺,1394b能提供800 Mb/s或更高的傳輸速度,雖然市面上還沒有1394b接口的光儲產(chǎn)品出現(xiàn),但相信在不久之后也必然會出現(xiàn)在用戶眼前,無論是在視頻傳輸還是在計算機外設、網(wǎng)絡互連等方而,都將有廣闊的市場。

評論