基于FPGA的MSK調制器設計與實現

經編譯后生成元件,其波形仿真圖如圖4所示,由圖可以得到:當start為低電平時,兩路輸出信號都為0;當start信號為高電平時,對輸入信號(datain_a)有:datain_a=011111111001,此時dataout_a=010101010001,對輸入信號(datain_b)有:datain_b=011110111101,此時Dataout_b=010100101001,由此可以得出,元件QDSP_PL實現了由絕對碼到相對碼的變換。

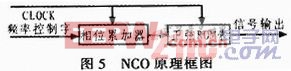

2.3 NCO的實現

2.3.1 NCO的實現原理

數控振蕩器在數字中頻中相對來說是比較復雜的,也是決定數字中頻性能的主要因素之一,NCO的目標是產生一個理想的正弦波或余弦波,如式(8)。

式中,fL0為本地振蕩頻率;fs為輸入信號的采樣頻率。正弦波樣本可以用實時計算的方法產生,但這只適用于信號采樣頻率很低的情況。在超高速的信號采樣頻率的情況下,NCO實時計算的方法是不可能實現的,此時,NCO產生正弦波樣本的最有效、最簡便的方法就是查表法,即事先根據不同正弦波相位計算好相應的正弦值,并按相位角度作為地址存儲相應的正弦值數據,工作時,在每輸入一個信號采樣樣本時,NCO就增加一個

2.3.2 相位累加器的FPGA實現

相位累加器由N位加法器與N位寄存器級聯構成。每來一個時鐘fc,加法器將頻率控制字K與寄存器輸出的累加相位數據相加,再把相加后的結果送至寄存器的數據輸入端。相位累加器輸出的數據就是合成信號的相位,當相位累加器累加到最大值時會產生一次溢出,完成一個周期的動作。溢出頻率就是NCO輸出的信號頻率。可用VHDL語言實現相位累加器的設計,其主要代碼如下:

評論