基于Xilinx-Spartan6 FPGA的MultiBoot設計的實現

4 MultiBoot實現簡例

實現MultiBoot操縱有兩種方法:(1)基于ICAP的寄存器編程實現。(2)通過在生成bit流文件時,設置相關選項實現。

4.1 基于ICAP的寄存器編程實現

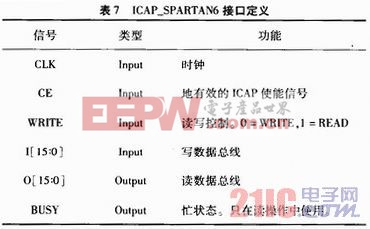

如上所述,通過ICAP_SPARTAN6原語發送IPROG命令,其發送命令序列如下:(1)發送同步字。(2)配置General1-General4,指定相關操作所需配置文件地址及操作碼。(3)發送IPROG命令。ICAP_SPARTAN6原語接口定義如表7所示。本文引用地址:http://cqxgywz.com/article/190467.htm

在主SPI模式下,ICAP_SPARTAN6的輸入數據在從總線I[15:0]輸入前,要進行字節范圍內的位交換,即16位寬的字分為高8位1 Byte,低8位1 Byte,各字節的最高位[7]和最低位[0]交換,位[6]與位[1]交換,其他以此類推。

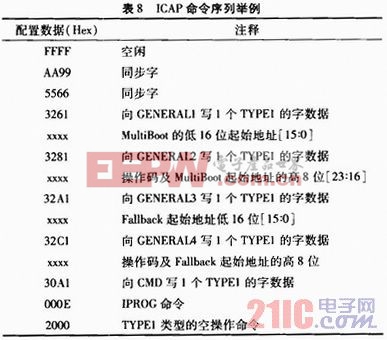

通過ICAP觸發IPROG的命令序列舉例如表8所示。

IPROG命令后需經過一段時間后,FPGA內部才會產生相應的重配置信號,因此在IPROG命令后需跟幾個空操作命令,一般為4個。GENERA L2、GENERAL4中的操作碼:0x0B、0x3B、0x6B分別為SPIx1、SPIx2、SPIx4。

ICAP邏輯模塊是FPGA中的專有邏輯模塊,因此在生成bit文件的各源文件中必須都實例化一個ICAP模塊。一般情況下對ICAP模塊的控制操作通過狀態機實現。

4.2 選項設置實現

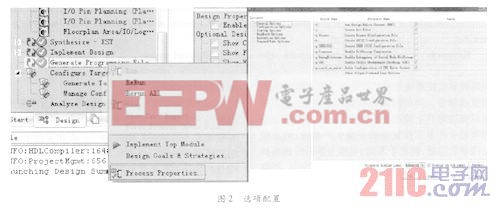

實現MultiBoot功能所需配置的所有寄存器,均可在生成bit文件時通過添加相關的生成設置選項實現。在進程菜單中單擊Generate Pro gramming File,選擇Process Properties,彈出配置窗口如圖2所示。

5 結束語

介紹了實現MultiBoot操作的兩種方式,一種是基于ICAP的寄存器編碼配置方式。可通過源代碼中的注釋,使后續開發維護人員閱讀代碼、擴展功能時思路清晰,缺點是需編寫大量代碼,并需對ICAP的操作與命令序列有一定了解。第二種通過在生成bit文時添加相關設置選項實現,方便簡單,但需大量的文本注釋,以便后續的開發與維護。當然,實際的應用開發過程中可同時使用這兩種方法,實現更高效便捷的編碼開發。

fpga相關文章:fpga是什么

評論