基于FPGA的NCO設計方案

4 設計實現及其仿真波形

本次設計采用性價比較高的ALTERA 公司的STRATIX芯片進行設計仿真,該系列芯片是基于1.5 V 工作電壓、0.13 μm全銅布線SRAM 工藝的FPGA 芯片。此系列芯片擁有最多114 140 個邏輯單元(Les)和最多10 Mbits 的內部RAM.該系列芯片支持多種I/O 標準,提供了最多可達12 個的用于處理復雜時鐘信號的鎖相環(PLLs)。同時,STRATIX 系列芯片提供了最多可達28 個的數字信號處理單元(DSP),它們由總共224 個內置硬件乘法器(9 位乘9 位)組成,利用它們可以有效地實現例如快速傅立葉變換(FFT)、有限沖擊響應(FIR)濾波器、無限沖擊響應(IIR)濾波器等高性能的數字信號處理單元或者乘法器。

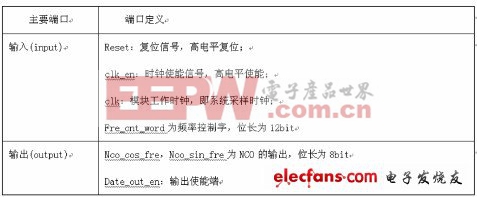

圖3 NCO 模塊的主要端口定義

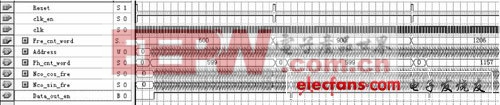

2)Quartus 仿真輸出波形,如圖4 所示。

圖4 NCO 的仿真輸出波形

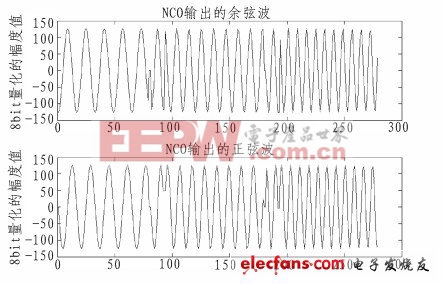

此仿真波形為3 個頻點的NCO 輸出波形, 用matlab 繪出輸出的載波的波形如圖5 所示。

圖5 輸出載波的波形

由上面的仿真結果可以看出,NCO 正確輸出了3 個頻點的仿真波形;同時通過實際的FPGA 硬件測試和驗證,該設計達到了所要求的性能指標。

5 資源占用情況

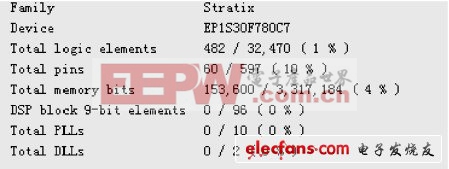

使用Altera 公司的STRATIX 芯片進行編譯、綜合,所得的資源占用結果如圖6 所示。

圖6 NCO 資源占用情況

6 結束語

本文給出了一種基于FPGA 的正交NCO 的設計方法,在實際應用過程中可參考給出的設計實例,通過改變頻率控制字、系統采樣頻率、存儲正余弦查找表的深度和存儲表的位寬,即可得到不同輸入頻率范圍的NCO;同時如果涉及需要的精度及頻率較高, 也可采用外置的存儲器, 如FLASH,SRAM 等與FPGA 配合使用, 較大的擴展存儲表的深度和位寬,可最終達到設計的要求。

fpga相關文章:fpga是什么

低通濾波器相關文章:低通濾波器原理

評論