基于FPGA的WALLACE TREE乘法器設計

4 乘法器的FPGA實現和仿真

在頂層乘法器WALLACE TREE邏輯架構設計中,可以通過描述語言模塊例化來調用前面手動實現的6:4壓縮器,可將slice壓縮模塊看成一個FPGA中固有的IP硬宏模塊,調用方法與使用FPGA器件內部的其他IP沒有區別。在FPGA Editer中對各個模塊相互位置按樹的層次和數字邏輯順序進行約束排列,形成一個約束文件。這樣FPGA芯片面積資源不僅得到充分的利用,在時序方面也會減小關鍵路徑的時延,提高時鐘頻率。

該乘法器的末級加法器要把WALLACE TREE得到的最后2個部分積快速的相加得到最終結果。末級加法器的實現方法有CPA(Carry Propaga tion Adder),該加法器的利用超前進位,可以使進位鏈這個關鍵路徑的時序在邏輯上層次減小。但該加法器在FPGA綜合實現后形成復雜結構,帶來的是利用了很大的布局面積和布線資源。FPGA內部結構中以其特有縱向結構的超級進位鏈,可將進位的器件延時和布線延時優化。可以利用該進位鏈,合理進行布局約束優化,使進位鏈路徑時序減小。實踐表明,在16×16的加法器中,該進位鏈的時延只有6 ns左右,大大減小了整個乘法器關鍵路徑延時。在圖4中列出了本設計的FPGA布局布線布局布線后仿真結果。該結果在XILINX-Virtex5-VC5VSX35T器件中運行,通過ModelSim仿真輸出采集。multin_a和multin_b分別是16位乘數,acc_out是相乘后輸出的32位結果,rst_n是復位清0信號。整個設計的硬件描述語言采用Verelog語言,其中例化了預先用FPGA Editer工具設計好的6:4硬宏壓縮模塊。本文引用地址:http://cqxgywz.com/article/190974.htm

圖5給出了WALLACE TREE乘法器設計的XILLNX-Virtex5-VC5VSX35T器件實際運行性能參數。該結果是FPGA器件以系統時鐘為120 MHz運行時,通過XILLNX公司ISE套裝軟件ChipScope采集獲取的數據。圖中,unt1和unt2采用FPGA內部一個測試計數器輸出的16位無符號乘數,將其輸入WALLACE TREE乘法器運算后,得到一組32位乘積結果。該實測結果表明,該結構的乘法器能工作正常工作在120 MHz系統時鐘的條件下,其實現電路關鍵路徑的延時小于8.33ns。

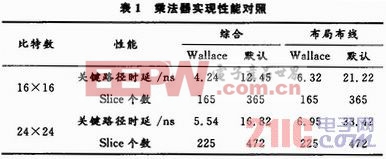

表1分別列出了16×16,24×24位乘法器在FPGA中用工具默認方法和本文方法生成的資源和時序對照圖。可以看出,本文的結構更合理,資源和速度都得到了一定程度的優化。

5 結語

本文根據FPGA內部標準單元結構,提出了一種改進的WALLACE TREE 6:4壓縮器的新型邏輯結構,并用Xilinx提供的工具套件FPGA Edi-ter實現了該壓縮器單元。結合乘法器在FPGA中的仿真表明,該結構的乘法器在提高系統的時鐘頻率和節省布局布線方面都有很大的優勢。

評論