全加器功能及應用的仿真設計分析

采用同樣的方法,將全加器本位和Si的真值表寫入邏輯轉換儀,操作邏輯轉換儀相應的圖標,可以準確地得到全加器本位和Si的標準與或表達式或最簡與或表達式,

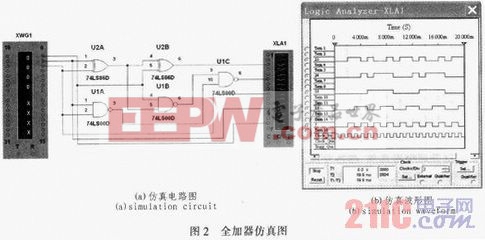

通過邏輯轉換儀設計出全加器的功能,進行仿真測試,如圖2所示。是根據設計得到邏輯表達式或邏輯圖,按照最簡仿真電路圖圖2(a),利用Multisim仿真軟件中字信號發生器XWG(Word Generator,又稱數字邏輯信號源)這個能產生32路(位)同步邏輯信號的儀器,用來對數字邏輯電路進行測試。XWG1產生全加器3個輸入變量的二進制邏輯組合。使用時,對字信號發生器面板上的各個選項和參數進行適當設置,才能使其正常工作和顯示。全加器仿真測試時參數設計地址為0000~0007、控制按循環輸出及逐個加1遞增方式編碼、選擇內部觸發方式、輸出頻率為1 kHz,作為電路信號。邏輯分析儀XIA(Logic Analyzer)可以同步記錄和顯示16路邏輯信號,用于對數字邏輯信號進行高速采集和時序分析。XLA1測試全加器輸入輸出的仿真波形,如圖2(b)所示,圖中波形從上至下分別是全加器輸出和Si、進位Ci、輸入Ai、Bi及低位進位Ci-1。從對應關系上觀察分析實際結果與理論設計相吻合,而且無競爭和冒險現象產生。從輸入變量波形的對應關系可見,字信號發生器XWG的輸出,隨著輸出端子號的增加頻率按照二分頻在衰減,如圖2(b)所示,每增加一個輸出端,頻率就衰減二分之一。所以在使用XWG時,輸入的對應關系一定要準確,否則就仿真不出結果。本文引用地址:http://cqxgywz.com/article/191007.htm

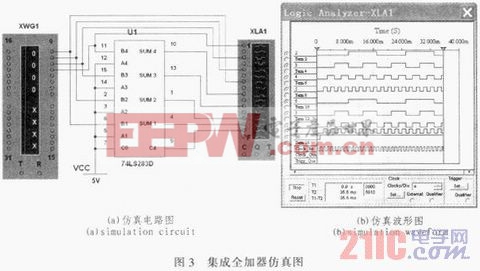

3.2 集成全加器仿真分析

在實際應用中廣泛采用的是集成全加器,代號74LS283。它是一個四位全加器,可以實現四位加法運算和功能擴展應用。全加器74LS283功能仿真電路如圖3(a)所示。為了能夠監測判斷出集成芯片的完好狀態,將兩個加數中的一個及低位進位均設置為高電平“1”接電源VCC,這樣全加器輸出的和就應該與另一個加數完全相同,仿真結果如圖3(b)所示。圖中從上至下分別顯示的波形是加數B4、B3、B2、B1,本位和S4、S3、S2、S1,最高位進位C4。仿真測試時字信號發生器參數設計地址從0000~000F,其余設置同上。圖3結果表明全加器74LS283的芯

片完好,功能準確。

評論