全加器功能及應用的仿真設計分析

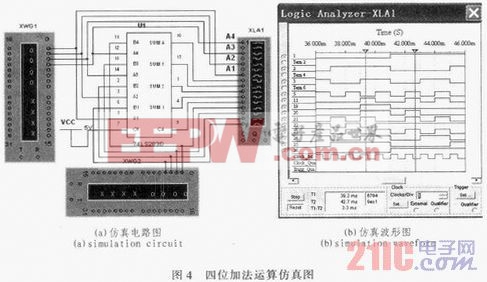

利用全加器74LS283芯片仿真兩個四位二進制數的加法運算電路圖,如圖4(a)所示。為確保兩個加數頻率變化不一致形成便于測試的輸入輸出結果,在與字信號發生器連接時把同一位的兩個加數接在不同的端子上,并設置好相應的參數,就能得到如圖4(b)所示的仿真波形圖。圖中從上至下波形是加數A4、A3、A2、A1,本位和S4、S3、S2、S1,最高位進位C4,另一個加數B4、B3、B2、B1。從仿真波形結果分析符合全加運算的規律和特點,滿足全加運算的結果。本文引用地址:http://cqxgywz.com/article/191007.htm

評論