基于FPGA的高速數據采集系統設計

2 硬件控制器的設計

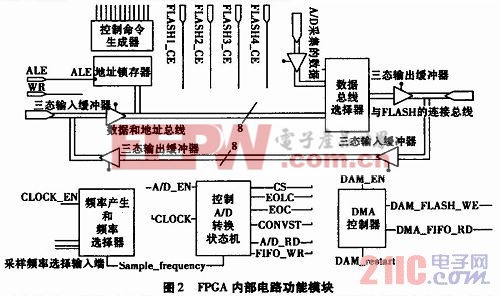

整個數據采集系統含有數據采集模塊和數據傳輸模塊。其中數據采集模塊由AD數據轉換模塊和Nandflash數據存儲模塊組成。系統采用USB接口做數據傳輸模塊,在此不作為本論文的重點進行描述。在數據傳輸部分本系統采用了DMA傳輸技術。其FPGA內部電路功能模塊如圖2所示。本文引用地址:http://cqxgywz.com/article/191012.htm

其中ALE,WR分別連接處理器的地址鎖存和WR引腳。而處理器設置成地址總線和數據總線分時復用的模式。這樣FPGA可以通過ALE信號來鎖存處理器的地址。而控制命令生成器用來譯碼產生相應的命令和操作。DMA控制器是我們自己編寫的特定的控制器,它需在收到處理器的DMA使能命令的情況下使得DMA_EN有效,然后在收到DMA開啟信號DMA_restart后,才會啟動一次DMA傳輸數據,每啟動一次傳輸一頁2 K的數據。在傳輸過程中,因為是多片FIFO的讀,為了數據不會亂,我們通過一個特定的控制器將DMA_FLASH_WE和多片FIFO的DMA_FIFO_RD匹配的統一起來產生了多片FIFO輪換讀的操作。

在采樣速率選擇的設計中,我們是應用先微處理器的軟件系統給FPGA的硬件系統一個采樣速率選擇值,而后FPGA的硬件系統內部將譯碼微處理器給的頻率值,頻率選擇器將根據這個數值產生相應的頻率輸出,頻率選擇器輸出的頻率又將輸入到控制AD轉換的狀態機里,這樣控制AD轉換的狀態機將根據輸入的頻率進行相應的頻率采集、數據的讀取和向FIFO寫數據等操作。

3 控制與存儲模塊

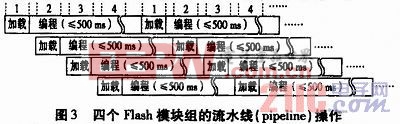

本系統在存儲方式設計時采用流水線操作方式。Nandflash存儲器的寫入有兩個階段:數據加載階段(即通過I/O端口將數據寫入頁數據寄存器)和編程階段(在芯片內部,將頁數據寄存器中的數據轉存到非易失性存儲單元內)。數據編程階段是自動進行的,不需要外部系統的其它操作,但它需要很長的時間,其典型值是200μs。而如果采用流水線存儲方式就可克服Nandflash芯片寫入速度較慢的缺點。應用流水線操作方式對Nandflash存儲器進行寫操作流程原理如圖3所示。首先對第一片Nandflash進行數據的加載,數據加載完后,第一片Nandflash隨后就將進入自動數據編程階段;然后再對第二片Nandflash進行數據的加載,數據加載完后,第二片Nandflash也將進入自動數據編程階段;然后依次對第三片Nandflash和第四片Nandflash進行相同的上述操作。而當第四片Nandflash數據加載完后,第一片Nandflash剛好已經自動編程數據結束,接著再從第一片Nandflash重復剛開始的加載數據和自動編程數據階段。就這樣如此循環一直到數據采集完成。這就是流水線的存儲方式。從整體時間來看,整個系統在一直的進行著數據的傳輸和存儲。

評論