IBIS 模型:利用 IBIS 模型研究信號完整性問題

輸入和輸出阻抗對信號傳輸至關重要。下列方程式定義了 IBIS 模型引腳的特性阻抗:

(6)

(6)輸出升降時間

在整個行業中,升降時間規范的慣例是使用輸出信號在 10% 和 90% 軌至軌信號之間擺動所需的時間,其一般為 0 到 DVDD。“IBIS 開放式論壇”的升時間定義相同,其獲得采用是由于 CMOS 開關波形尾部較長。本文引用地址:http://cqxgywz.com/article/191016.htm

IBIS 模型內的輸出、I/O 和三態模型,有一些位于“[Ramp]”關鍵字下面的規范,該關鍵字針對 R_load (test load)、dV/dt_r (rise time) 和 dV/dt_f (fall time)。升降時間數據范圍為電壓-輸出信號的 20% 到 80%。如果典型 dV/dt_r 值的分母乘以 0.8/0.6,則升時間值將在 20%-80% 擺動到 10%-90%擺 動之間變化。請注意,該數據代表一個電阻性負載 (R_load) 的緩沖器。ads129x.ibs 文件中,DIO_33 數據假設為一個 50-Ω 負載,因此該數據未達到 DVDD。該計算產生的數值,為各種傳輸線計算提供了正確的 tRise 值,例如 fKnee、f3dB 和升沿長度。

利用 IBIS 設計傳輸線

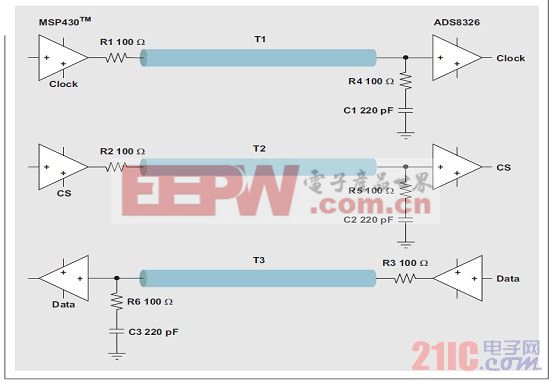

本文以討論一個錯配端接阻抗的 PCB 作為開始。之后,我們通過 IBIS 模型,了解和查找這種傳輸問題的一些關鍵組成元素。就此而言,這種問題應該有解決的方案。圖 7 顯示了端接校正策略,而圖 8 則顯示了校正之后的波形。

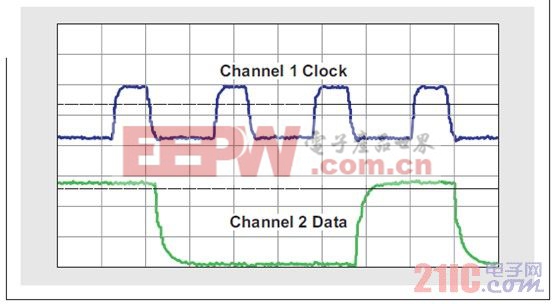

圖 8 端接校正的穩定信號

若想設計 PCB 傳輸線,第一個步驟便是從產品說明書收集資料。第二個步驟是檢查 IBIS 模型,找到無法從說明書中獲取的一些參數—輸入/輸出阻抗、升時間和輸入/輸出電容。在進入到硬件階段,需利用 IBIS 模型找到一些關鍵的產品規范,并對最終設計進行仿真。

評論