基于FPGA的FIR數字濾波器的優化設計

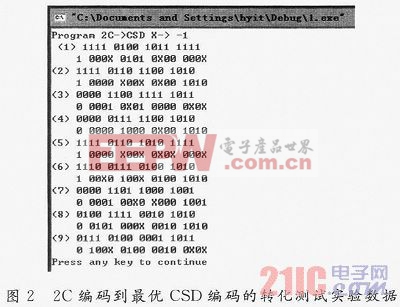

測試實驗數據及結果如圖2所示。在本C語言程序中用X來指代碼,輸入數據為16位。本文引用地址:http://cqxgywz.com/article/191069.htm

4 實例設計過程與仿真

4.1 FIR系數提取

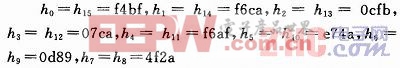

利用Matlab中Fdatlool設計一個16階低通FIR濾波器,各項性能指標為:采用頻率fs=48 kHz,截止頻率fstop=12 kHz,通帶寬度fpass=9.6 kHz。系數數據寬度為16位;輸出數據寬度是16位。為了便于FIR濾波器的FPGA實現,減小誤差,將Fdatlool提取的濾波器的系數量化取整后為:

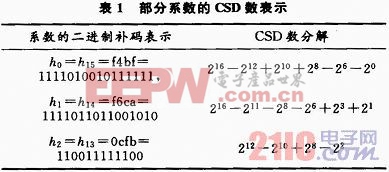

4.2 系數的CSD轉換

讀入量化系數,進行CSD轉換操作,生成CSD碼,表1是部分量化后的系數及對應的CSD數。

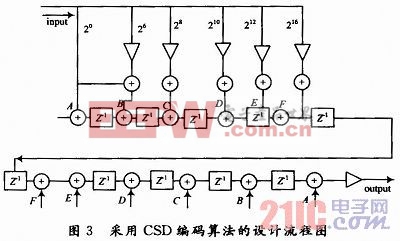

4.3 FIR濾波器實現結構

采用轉置形式的FIR濾波器結構,此結構和直接型結構不同的是,輸入信號X[n]是同時分別和濾波器系數向量相乘,不需要通過不同的延時單元再和相對應的濾波器系數相乘。這種結構最大的優點是工作頻率較高,圖3給出了采用CSD編碼算法的設計流程圖。

評論