JPEG2000中5/3離散小波多層變換FPGA實現研究

3.2 地址生成模塊的設計

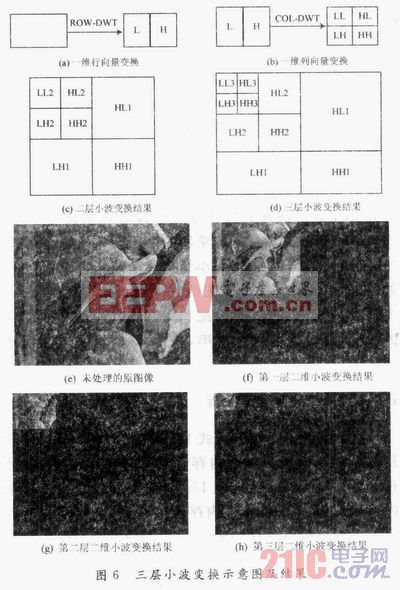

對于做三層的離散小波變換,每層對RAM的(行/列)讀/寫地址都不相同,所以在地址生成模塊中分別做了三層各自的地址模塊,每個單層地址模塊產生2路讀地址信號、2路寫地址信號和1路寫地址使能信號。首先產生行變換的讀/寫地址,在行變換完成之后產生列變換的讀/寫地址,在列變換完成之后,給出一個EndOfBlock信號返回給圖4中的Control模塊。由Control模塊控制分層地址模塊的使能以及Select模塊選擇有效地址信號輸出,并且通過對讀地址計算算法的調度,實現分裂和邊界延拓功能,不需要另外設計單獨的處理模塊,地址生成模塊的總體框圖如圖4所示。

4.功能仿真及FPGA測試驗證

該設計采用了流水線技術即通過插入寄存器,使得一組輸入數據的計算分布在同一個時鐘周期中,從而提高資源利用率,增加電路的數據處理量,提高了性能,在此用Verilog HDL描述實現。

4.1 功能仿真

在ModelSim的測試模塊中設置時鐘為100 MHz,圖5為部分仿真結果,輸入數據在經過3個時鐘周期后計算出LH分量輸出。由此可見,一維小波變換模塊的設計符合JPEG 2000標準規定,結果正確。本文引用地址:http://cqxgywz.com/article/191091.htm

評論