線性調頻信號基于FPGA IP核的脈沖壓縮設計

2 脈沖壓縮系統設計

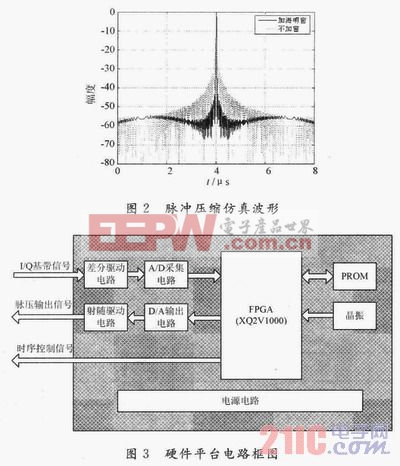

該系統的主要功能是對線性調頻I/Q基帶信號進行高速采集,然后在FPGA中實現線性調頻信號的脈沖壓縮,之后通過D/A變換器輸出脈壓結果,監測脈壓后的波形。

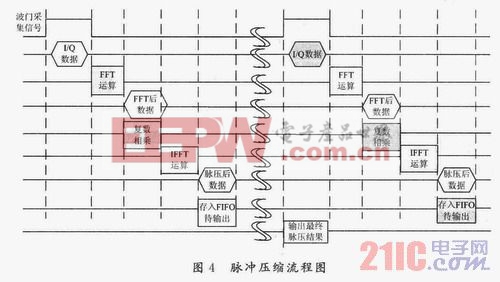

2.1 系統硬件平臺

該系統硬件平臺主要包括:差分驅動電路,A/D采集電路、FPGA電路、晶振等電路、電路結構框圖如圖3所示。本文引用地址:http://cqxgywz.com/article/191135.htm

FPGA采用的是Xilinx公司的芯片XQ2V1000,其配置芯片為Xilinx公司的PROM芯片XQ18V04,以主動串行方式對FPGA進行上電配置。差分驅動電路選用ADI公司的AD8138,A/D、D/A電路分別為ADI公司的14位高速模/數轉換芯片ADS5500和14位高速數/模轉換芯片DAC5675A。硬件電路的設計注重細節:I/Q兩通道傳輸線設計時保證線長相等,使得I/Q時延帶來的相位誤差一致;采用DCI(DigitaUy Controlled Impe-dance)端接技術,在FPGA的每個bank上外接兩個參考電阻來對該bank的每個I/O管腳實現端接,減少外接電阻的數量,實現阻抗匹配,提高系統的穩定性;做好電源濾波,對元器件進行合理布局,布線,對模擬信號和數字信號進行有效隔離,減小信號間串擾。

2.2 軟件設計流程

整個脈沖壓縮處理在時間上是順序的,是典型的數據流驅動的系統,即先進行FFT,復乘然后是IFFT及FIFO輸出,脈沖壓縮的總時序關系見圖4。該系統實現1 024點的脈沖壓縮,算法上采用基于IP核的設計方法。主要用到了FFT核,乘法器核以及單口Block Memory核,這些IP核的應用及脈沖壓縮的具體實現如下所述。

評論