基于FPGA的SoC原型驗證的設計與實現

(4)Scatter文件部分。scatter文件是用來描述刪連接器生成映像文件時需要的地址映射信息和加載域信息。本文引用地址:http://cqxgywz.com/article/191152.htm

下面以UART模塊為例,在此框架下根據其接口編寫相應的測試程序。

驗證計劃:通過待驗UART與PC進行通信來驗證其功能是否正確,主要驗證的功能點有:1)寄存器讀寫;2)三種工作模式普通模式、自流控模式、LoopBack模式;3)奇偶校驗;4)波特率;5)FIFO觸發級。

測試程序:根據上邊的功能點可以劃分兩個測試的基本的函數,一個是寄存器讀寫的測試函數UART_RWTst(),還有一個就是UART工作配置函數UART_Config(),這個函數提供一個接口,通過這個接口可以配置UART的工作模式、奇偶校驗方式、波特率大小、FIFO觸發級。在更高層的測試應用程序中調用配置程序,變化配置參數,使其與PC進行收發數據,然后查看或比對數據,判別其功能是否正確。測試程序文件結構如圖5所示。

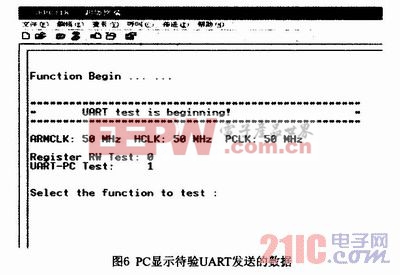

驗證結果:當待驗UART向PC發送數據時,在PC的超級終端會顯示這些數據,UART功能驗證結果可通過觀測或數據比對來判斷,如圖6所示。

4 結論

同樣的測試激勵程序在此原型平臺的執行速度要比SDV(Software driven verification)平臺快4~6個數量級。本驗證平臺的搭建過程中對其進行了形式驗證和時序分析,大大減少了在原型設計中由于FPGA實現而導致的錯誤。本平臺的軟件測試程序具有接口簡單、易調試、可重用性好等特點,筆者在此原型平臺下完成了部分模塊的驗證,有效地提高了驗證效率,縮短了項目的開發周期,加大了流片成功率。

評論