基于FPGA的部分響應CPM信號解調器的設計

(2)加比選ACS 模塊

此模塊分為兩部分:①計算路徑度量值;②選擇當前時刻最佳路徑。當前狀態的路徑度量值為該狀態下所有可能的路徑度量值中的最大值。最佳路徑為最大路徑度量值對應的上一狀態。在設計中采用確定CPM 調制的起始狀態的方法。

復位時將起始狀態的路徑度量值賦值為0;將其他狀態的路徑度量值賦值為一個較小的負數。采用這種方式有效避免解調時起始狀態的不確定性。

CPM 的解調在一定的譯碼數量后,路徑度量值的存儲器便會飽和溢出。該設計采用一種簡單方法防止溢出:每次路徑度量值計算完成后,判斷其最大值,如果最大值超過某一確定的正值,則所有的路徑度量值減去一個正值。再判斷是否有度量值小于一個確定的負數,如果有,則將其值重新賦值為一個較小的負數。仿真中,證明了這種方法的可行性。

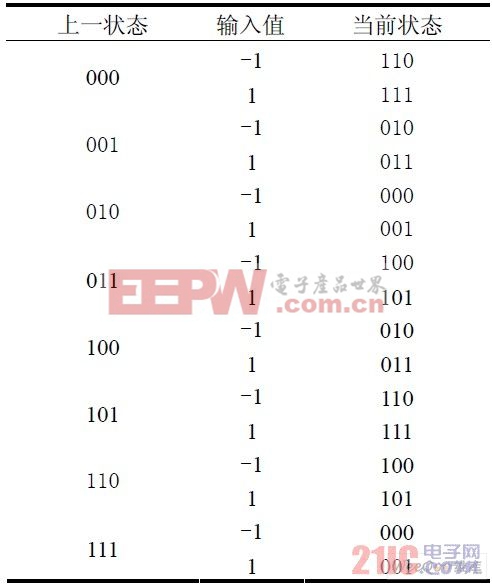

表1 輸入數據與狀態間轉移關系

(3)回溯模塊

此模塊包括幸存路徑存儲和判決輸出。在模塊中比較當前時刻各狀態的路徑度量值,求得最大路徑度量值,以及對應的當前狀態。從表1 可知,狀態的最低位可以表現上一時刻的輸入值,最低位為0 時,表示上一時刻的輸入碼字為-1;最低位為1 時表示上一時刻的輸入碼字為1。

3 硬件實現、時序仿真和性能

這里選擇的FPGA 是Xilinx 公司的Virtex5 系列的XC5VSX95T 芯片,設計軟件為ISE, Synplify, Modelsim,Matlab,設計語言采用VHDL 硬件描述語言。

評論