基于FPGA的跳擴頻信號發送系統設計

2.3.2 跳頻圖案設計

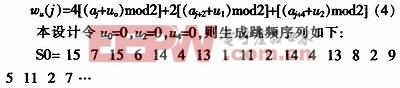

跳頻圖案采用對偶寬間隔跳頻序列,基于m序列,利用非連續抽頭(L-G)模型,構造寬間隔跳頻偽隨機序列,自相關性能、互相關性能較高接近最佳跳頻序列族,提高信號的抗干擾性。設計中基于L-G模型的非連續抽頭模型,采用本原多項式

跳頻序列由FPGA生成并按寬間隔對偶要求輸出如圖6所示。本文引用地址:http://cqxgywz.com/article/191295.htm

2.3.3 跳頻硬件架構

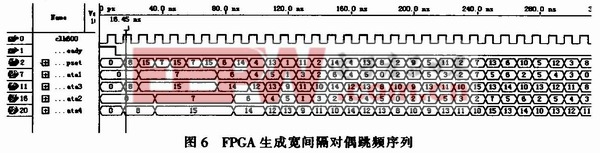

跳頻硬件電路核心是AD9951,硬件連接如圖7所示。該芯片內置400MS/s時鐘,內含14位DAC,相位、幅度可編程,有32位頻率控制字、相位偏移字,可用串行I/O控制,采用1.8V電源供電,可4~20倍倍頻,支持大多數數字輸入中的5 V輸入電平,可實現多片同步。通過送入設置,送入地址碼和跳頻碼,實現信號的跳頻產生。AD9951控制時序如圖8所示。

評論