基于FPGA的語音存儲與回放系統設計

2.3 模數轉換(ADC)電路

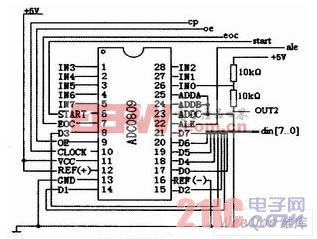

ADC電路如圖4所示。題目要求采樣頻率fs=8kHz,字長=8位,可選擇轉換時間不超過125 μs的8位A/D轉換芯片,ADC0809的轉換時間為100μs,可選用ADC0809。音頻信號經過放大、濾波送給ADC0809 ADC電路,將模擬量轉換為數字量,再經可編程器件送給存儲芯片。cp、oe、eoc、start、ale、din[7..0]接圖9。

圖4 ADC電路

2.4 語音存儲電路

存儲芯片HM628128D管腳如圖5所示。HM628128D可存儲8位131072字,5V供電,靜態RAM。語音存儲時間≥10s。HM628128D在數字化語音存儲與回放系統硬件電路中的接線如表1所示。HM628128D讀寫功能如表2所示。

圖5 HM628128D管腳

2.5 數模轉換(DAC)電路

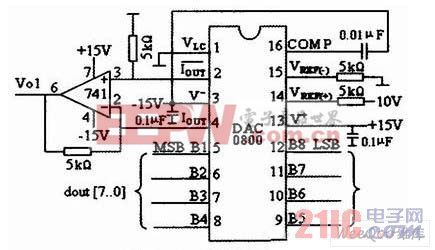

DAC如圖6所示。題目要求變換頻率fc=8kHz,字長=8位,可選擇轉換時間不超過125μs的8位D/A轉換芯片,DAC0800的轉換時間為100ns,可選用DAC0800。存儲芯片輸出的數字量經可編程器件圖9送給DAC0800 DAC電路,將數字量轉換為模擬量。

圖6 DAC0800 DAC電路

評論