基于FPGA的視頻采集與顯示模塊設計

2 圖像采集和Video_to_VGA模塊設計

由ADV7181輸出的itu_r65*:2:2格式的視頻數據流格式如圖2所示。圖中, EAV和SAV為兩個基準信號, 要想獲得有效視頻數據, 就得首先檢測到SAV。操作時, 首先要對FF0000進行檢測, 然后再根據XY提取F、H來判斷SAV基準信號。XY一般由8位數據組成, 圖3所示是其位格式表示。

圖2 itu_r65*:2:2格式視頻數據流

圖3 XY各位表示

2.1 ITU_R656_DECODER模塊設計

圖3中, XY的第七位為場信號, F為0表示第一場, F為1表示第二場; XY的第六位為場消隱信號, V為0表示數據是有效信號, V為1表示數據處于場消隱階段; XY的第五位為有效數據開始結束信號, H為0表示有效視頻數據開始信號,H為1表示有效視頻數據結束; 而P0、P1、P2、P3為保護比特。操作時首先要檢測FF 00 00, 然后提取F、V、H等信號, 最后再根據這些信號信息對視頻數據進行相應的處理。圖4所示是本圖像采集系統的總體框圖。

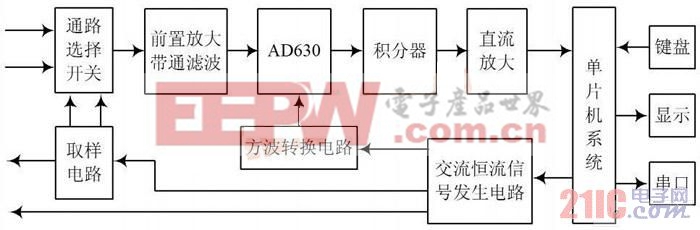

圖4 系統總體框圖

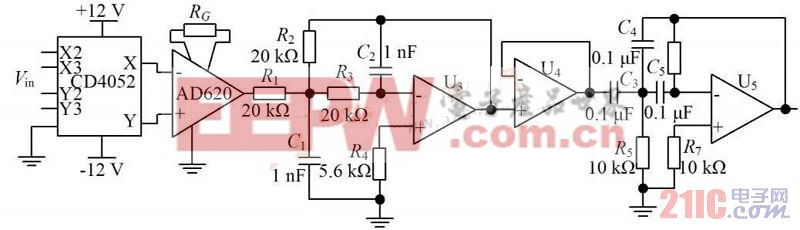

Video_to_VGA 模塊主要由ITU_R656_DECODER模塊和YCbCr2RGB模塊組成, 這里先對ITU_R656_DECODER模塊進行設計。圖5所示是ITU_R656_DECODER模塊的設計原理框圖。

設計時, 首先應構建串轉并模塊, 以便對有效信號中的串行YCbCr信號進行分離, 然后對亮度色差信號分別進行處理, 以同時產生field和13.5M的Ypix_clock信號; 接著對TD_HS進行倍頻以產生HSX2, 再通過三個dui_port_c1024模塊將4:2:2的視頻信號轉換為4:4:4的視頻信號。其中,在dui_port_c1024模塊中使用乒乓操作, 以實現對數據的連續處理, 讀時鐘為寫時鐘的2倍, 即寫入一行數據, 讀出后變為兩行, 這樣可實現奇行代替偶行, 從而實現去交織(由于人眼對奇行偶行數據分辨力較差, 故允許這種處理方式),輸出的Y, Cb, Cr用于后期所要使用的10位RGB信號, 而Ypix_clock、HSX2和VSX1則用于產生VGA的時序信號。

評論