FPGA 電路動態老化技術研究

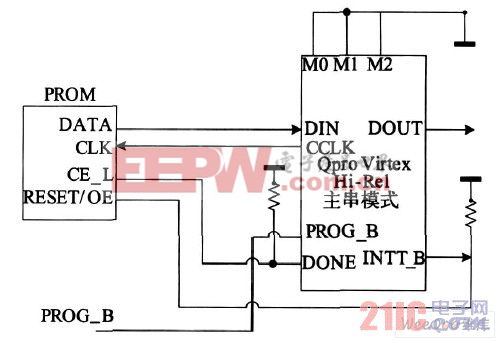

主串模式電路連接圖見圖1。

圖1 FPGA 配置主串模式連接圖

系統或芯片上電后,信號引腳PROG_B被拉低,FPGA的配置RAM存儲器清空;同樣,PROG_B上的邏輯低電平將會復位配置邏輯,并使FPGA 保持在清空配置存儲器狀態。只要PROG_B 引腳保持低電平,則FPGA 將繼續清空它的配置RAM存儲器,并使INIT_B 信號保持為低電平以表明配置在被清空。

當PROG_B被釋放時,FPGA將繼續使INIT_B保持低電平,直到完成清空所有的配置存儲器。FPGA 在INIT_B信號的上升沿檢測其模式引腳M0、M1、M2。

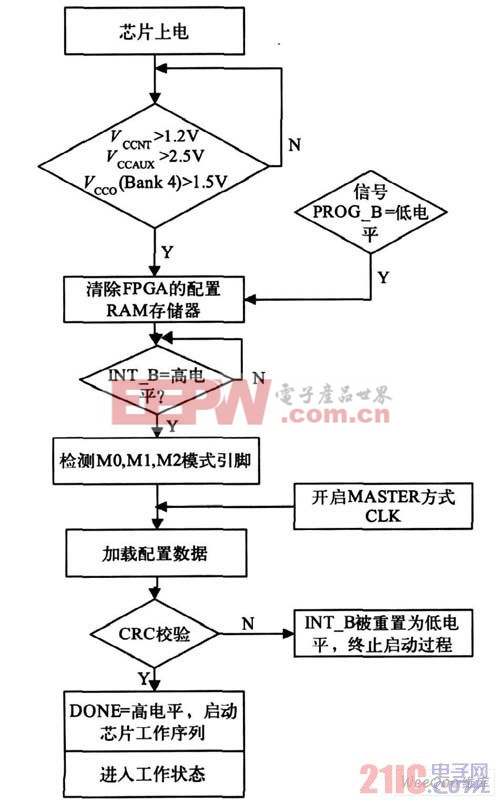

INIT_B 信號變為高電平后,配置就可以開始了,不需要額外的暫停或等待周期。但是,配置過程不必在INIT_B 變化之后就立即開始。配置邏輯只有當位流的同步字被載入時才開始處理數據。當上電清除配置RAM存儲器后,INIT_B信號引腳變高電平,可以開始載入配置數據:標準的位流首先是引入空閑字FFFFFFFFh,其次是同步字AA995566h,然后是一些配置控制信息,緊跟其后的才是真正的位流數據幀和相關的CRC;位流的最后是CRC 校驗和啟動芯片進入工作態。FPGA 電路配置流程圖如圖2 所示。

圖2 FPGA 電路配置流程圖

DIY機械鍵盤相關社區:機械鍵盤DIY

評論