采用MAX II器件實現FPGA設計安全解決方案

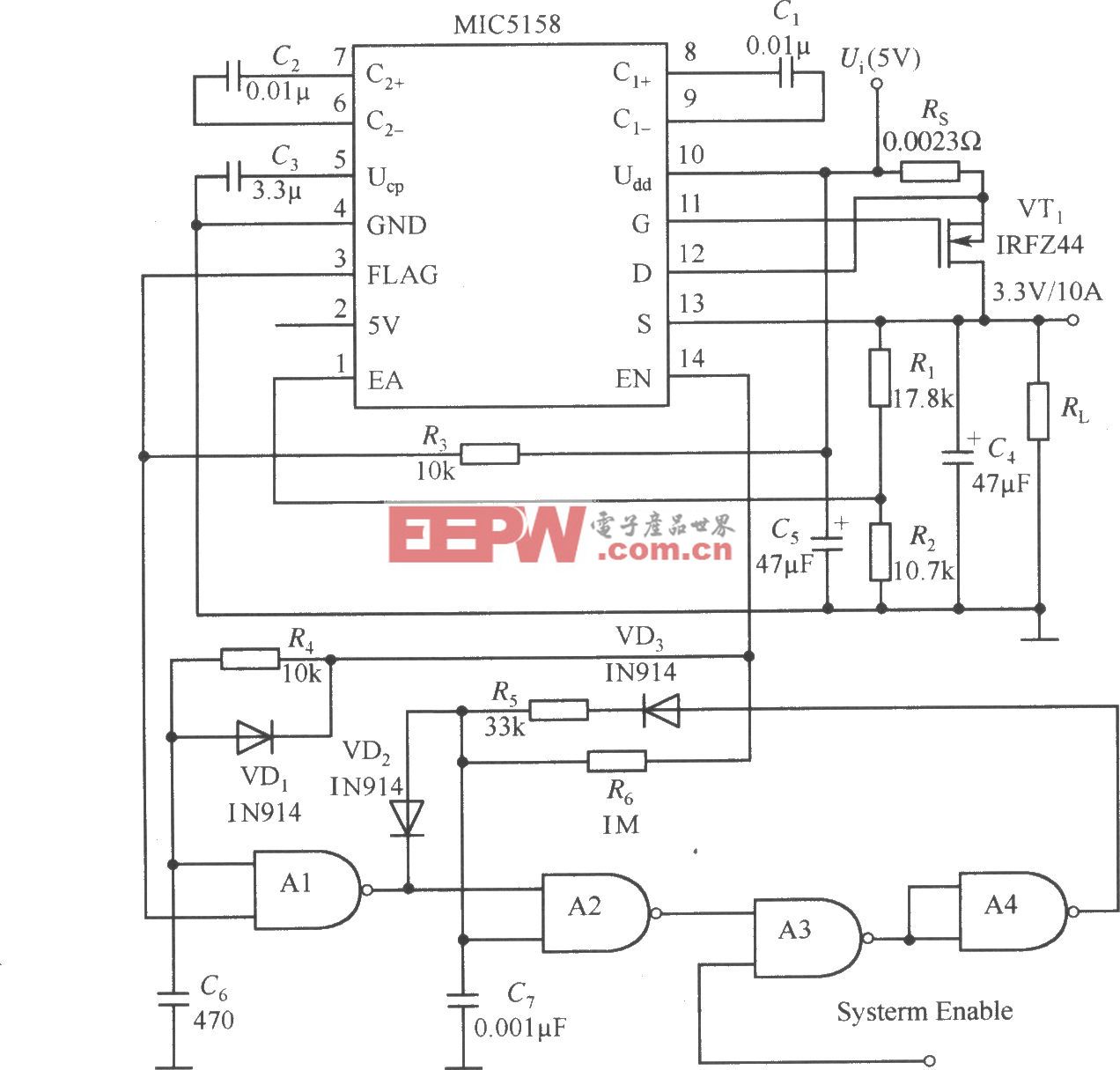

1、時鐘分頻器FPGA中的時鐘分頻器用于從系統時鐘產生速率較低的時鐘,供給FPGA和MAX II器件的安全內核使用。這是因為安全內核不需要運行在非常高的頻率下。特別是當系統運行頻率非常高時,時鐘分頻器的作用便比較顯著,否則,如果系統運行頻率較低,可以不使用該分頻器。

2、隨機數發生器(RNG)每次啟動/復位信號置位時,RNG為64位計數器產生隨機初始值。然后,隨機數同時串行移位至FPGA和MAX II器件的安全內核。參考設計采用32位RNG。

3、隨機數接收器隨機數接收器接收來自RNG的串行隨機數,并按照正確的順序排列數據,將其做為初始值送入64位計數器。

4、64位計數器64位計數器用于產生送入編碼器的64位數據。它是按照公式X=X+A進行的一個簡單加法器。X是一個64位初始值,而A是計數器遞增值,應為質數。初始值X來自RNG。參考設計中,32位來自RNG,其余32位由用戶在設計代碼中設置。A可以由用戶在設計代碼中設置。計數器輸出送入編碼器,對數據進行加密。編碼器每次完成前一數據的加密后,計數器數值遞增。

5、編碼器編碼器可以采用任何難以破譯的加密標準。參考設計采用了三重數據加密標準(3DES)。3DES編碼器的輸入和輸出是64位值,需要48個時鐘周期完成64位數據加密。

6、移位器/復用器移位器/復用器將編碼器輸出比特(16位)的一部分按照特定順序,存儲在寄存器中,編碼器準備下一數值時,將其串行移位至比較器。

7、比較器比較器將MAX II器件的編碼數據(握手令牌)與FPGA內部產生的編碼數據逐位比較。如果MAX II器件和FPGA的數據相匹配,Enable信號置位,使能用戶設計功能。如果出現不匹配,請參見下面的可靠性保證一節。這種方式可以重復幾次,以產生更多的Enable信號,使能用戶設計的不同部分。這種重復方式可以防止有人篡改FPGA比特流(這種可能性較低),致使Enable信號變為高電平,導致設計安全方案失效。

8、可靠性可靠性部分處理隨機比特錯誤,這種錯誤可能會導致系統停止工作。參考設計允許每10個時鐘周期中出現一次數據不匹配(這僅僅是一個例子,用戶可以根據實際應用,修改該方法,達到最佳效果)。換句話說,如果10個時鐘周期中,數據不匹配不超過一次,Enable信號仍將保持高電平,系統繼續工作。如果10個時鐘周期中出現兩個錯誤,那么,Enable信號變為低電平,禁止用戶設計功能。在啟動/復位信號置位,復位系統前,系統停止工作。

圖3:不支持安全方案的FPGA設計。

分頻器相關文章:分頻器原理

評論