微型打印機與FPGA的硬件接口及軟件設計

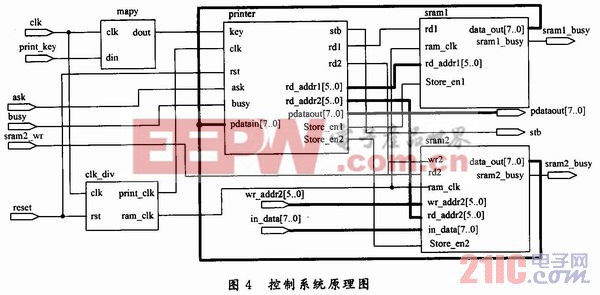

軟件設計在FPGA內部綜合生成2個內部存儲器,表頭數據存儲于一個存儲器中,對現場采集的數據獨立保存于另一個存儲器中,根據判別條件,由打印機控制模塊分時讀出存儲器的數據并寫入打印機顯示。控制系統原理如圖4所示。

圖4中,mapy模塊是按鍵防抖動模塊,clk-conv是時鐘分頻模塊,得到打印控制塊和隨機存儲器所需的時鐘。隨機存儲器SRAM1和SRAM2是利用FPGA內部資源綜合生成的,SRAM1中固化好了打印數據的表頭數據,只需控制讀即可。設計中為了編程方便,僅僅將SRAM2源碼稍作修改即生成 SRAM1,實際可以設計ROM代替。SRAM2用來存儲打印機前端數據采樣與處理單元處理的數據,并在打印控制模塊(printer)的控制下,分時送入打印機緩存。打印控制模塊是核心,它不僅查詢打印機的工作狀態,控制打印機打印緩沖區數據,還負責讀出SRAM中的數據,并寫入打印機。

2.3 系統功能仿真與分析

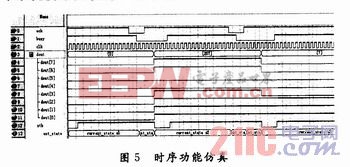

微型打印機控制塊(圖4中printer塊)的功能仿真圖如圖5所示。clk是系統時鐘,busy,ack,stb,dout是微型打印機的并行接口信號,currem_state表示工作時狀態之間的轉換關系。由圖可以看到,當busy=O時,狀態sO進入s1,系統對stb置位后,數據由dout輸出,狀態轉移到s2,s2有足夠的延時;當ack為低電平時,狀態轉移回到s0狀態,等待下一次數據傳輸。實際上數據在s1狀態時就應該輸出,但是圖中所示卻在s2狀態開始時輸出,這是因為設計有限狀態機時,采用的是莫爾狀態機的基本思想,它屬于異步輸出狀態機,輸出僅僅為當前狀態的函數,所以這類狀態機在輸入發生變化時還需要下一個時鐘的到來。打印機實際打印效果如圖6所示。

3 結語

利用VHDL硬件描述語言設計系統軟件,通過FPGA控制微型打印機工作。本微型打印機與FPGA組成打印系統后,FPGA將顯示數據寫入FPGA內部設計的SRAM中,FPGA與微型打印機進行數據交換后,將欲打印數據讀出并與控制命令一起按打印順序送到微型打印機打印緩沖區中,完成打印輸出。設計的打印系統攜帶方便,實時性高。

本文引用地址:http://cqxgywz.com/article/191405.htm

評論