基于FPGA的線性卷積的實時實現

觀察圖8可知,經過FFT變換和IFFT變換以后的累積相對誤差保持在±3%以內,主要原因是FPGA計算FFT和IFFT過程中由于精度的要求,進行數據舍去,造成誤差的產生。這種誤差是由硬件客觀條件限制的,不可避免,但是±3%的誤差精度完全可以滿足實際應用。

本系統由于涉及到高速A/D、高速D/A,所以在PCB設計過程中必須考慮電磁兼容EMC(Electro Magnetic Compatibility)和抗電磁干擾EMI(Electro Magnetic Interference)性和信號的完整性。總體來說,在進行高速PCB設計過程中,不僅要考慮PCB的元器件布局和布線,同時設計中的接地、去耦和旁路同樣重要。例如在A/D部分這種混合信號PCB設計中,由于混合了模擬信號與數字信號,只有盡可能減小電流環路的面積才能降低數字信號與模擬信號之間的相互干擾。一個可行的方法是將地平面分割,然后在A/D轉換器下面將模擬地和數字地連接在一起。

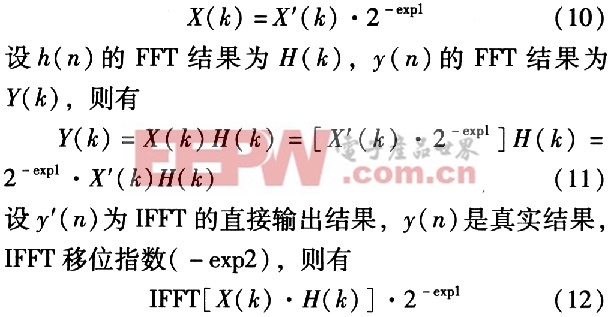

在處理FFT和IFFT核的指數問題時,正常做法是在FFT結束后直接做一次指數調整,在IFFT結束后再做一次指數調整。設經過FFT核后的直接輸出結果為X’(k)、對應指數輸出為(-expl),x(n)的真實結果為X(k),則有

由式(12)可知,FFT和IFFT的兩次指數調整實際可以在IFFT合為一次,可以減少控制的復雜程度。兩次調整指數的示意圖如圖9所示。一次調整指數的示意圖如圖10所示。

6 結束語

本文基于Altera的FPGA EP2S60F1 020C8,搭建了結合A/D,D/A等功能的配套處理平臺,完成了對高速離散卷積的硬件實現,使該系統在100 MHz時工作正常,滿足了設計要求。同時,分析了影響處理速度的多個方面,提出了對應的改進方法,為系統的升級提供了依據。隨著電子技術的發展,更高性能的FPGA處理芯片的出現和各種商業IP核的技術升級,本文提出的高速卷積的硬件實現方法在速度和靈活性等方面均逐漸展現出優越性。

評論