基于FPGA的時間間隔測量模塊設計

4 功能實現及仿真

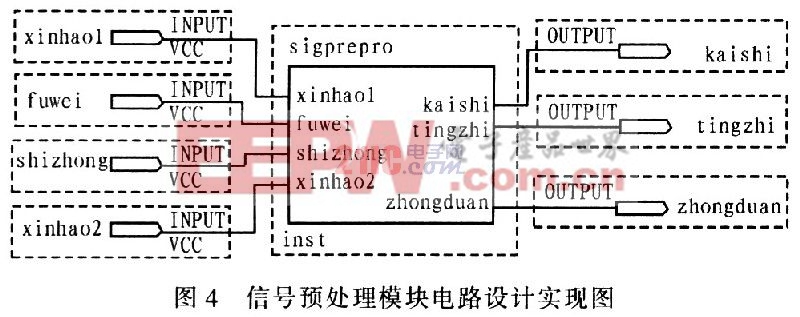

通過QuartusⅡ開發環境,文本編輯方式,用VHDL語言進行編程,生成圖元,結合頂層原理圖設計,實現信號預處理模塊原理圖,如圖4所示。

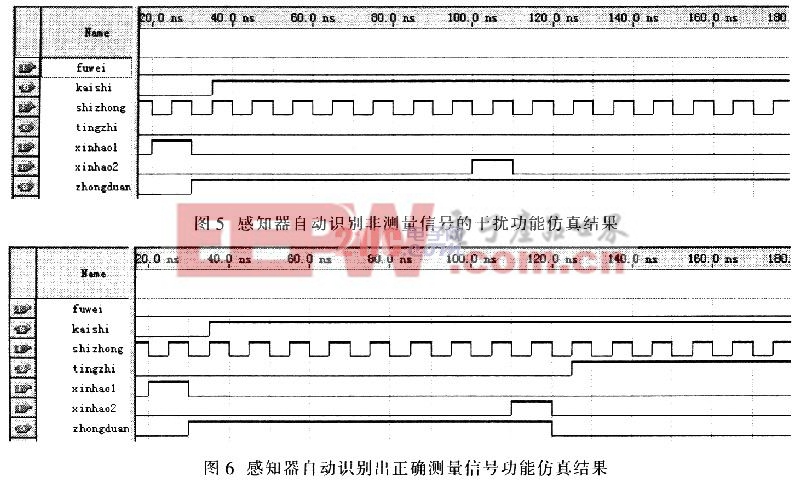

對編寫的程序進行調試、編譯通過,然后進行功能時序仿真,實現如果信號2到來之前已經收到信號l,并且已經在計數,但若小于預設的閘門關閉時間80 ns,則不進行閘門關閉。即中斷保持高電平不變,停止信號保持低電平,感知器認為此信號為非測量信號2,繼續監測信號2的到來,如圖5所示。

如果信號2到來之前已經收到信號1,并且已經在計數,但若大于或是等于預設的閘門關閉時間80 ns,則進行閘門關閉,即中斷由高電平跳變為低電平,停止信號由低電平跳變為高電平,感知器判斷出此信號為所要測量的信號2,通知主控制器讀取數據,如圖6所示。

5 結論

該系統硬件設計采用Ahera公司的FPGA器件EPIC3T10017,同時軟件設計采用其公司自行開發的QuartusII開發環境進行程序設計及其功能時序的仿真。實踐表明,由于FPGA器件簡單易學,市場占有量大,開發設計人員容易購置,開發技術易于掌握,尤其是FPGA本身功能強大,故其在工業控制領域中將占據重要的位置。這里所介紹的時間間隔測量技術可在靶場測試、激光測距、物理實驗、航空航天等領域發揮良好的作用。

評論