FPGA芯片在高速數據采集緩存系統中的應用

摘要:給出了以FPGA為核心邏輯控制模塊的高性能數據采集系統的設計方法,并在QuartusII8.0集成環境中進行軟件設計和系統仿真,最后給出了新型緩存系統中主要功能模塊的仿真圖形。

關鍵詞:FPGA;高速;數據采集;緩存

0 引言

在高速數據采集方面,FPGA有單片機和DSP無法比擬的優勢。FPGA的時鐘頻率高.內部時延小,全部控制邏輯都可由硬件完成,而且速度

快,組成形式靈活,并可以集成外圍控制、譯碼和接口電路。更最主要的是,FPGA可以采用IP內核技術,以通過繼承、共享或購買所需的知識產權內核提高其開發進度。而利用EDA工具進行設計、綜合和驗證,則可加速設計過程,降低開發風險,縮短了開發周期。效率高而且更能適應市場。本數據采集系統就是基于FPGA技術設計的多路模擬量、數字量采集與處理系統。FPGA的10端口多,且可以自由編程、支配、定義其功能,同時配以verilogHDL語言以及芯片自帶的可定制模塊,即可進行軟件設計。FPGA的最大優點是可在線編程。此外,基于FPGA設計的數據采集器還可以方便地進行遠程功能擴展,以適應不同應用場合的需要。

1 系統基本構架

本文所設計的高速數據采集系統是某雷達信號處理系統的一部分,可用于雷達信號的預處理以及采集、緩存。本系統以高速FPCA為核心邏輯控制模塊,并與高速ADC和DSP相連接。其系統基本架構如圖1所示。

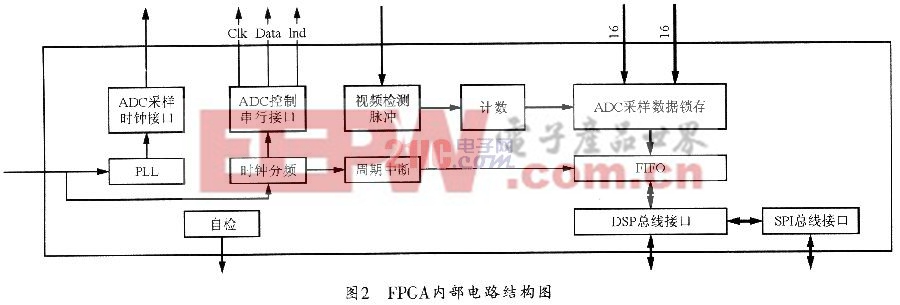

圖l中的FPGA可用作數字接收機的預處理模塊,該器件集成有PPL倍頻、ADC控制接口、FIFO及其管理、SPI接口、DSP總線接口、狀態和自

檢模塊等。FPGA的內部結構功能框圖如圖2所示。

圖2中的中斷產生模塊用于產生周期性中斷,利用視頻包絡和100 MHz時鐘可形成50 MHz的DMA同步傳送時鐘,然后通過外部口DMA方式將

采樣數據傳送到DSP。ADC控制串行接口為通用三線串口,SPI總線接口實際上是一個串并轉換器,可用于控制本振。本系統的DSP數據總線為

64位寬度,地址為32位。

由于雷達信號接收機中的信號處理量大,信號復雜,因此,通過基于高速大容量FPGA芯片的實時數據采集系統可以很好的滿足對信號預處理的需要。

評論