基于CPLD的異步串行通訊控制器的研究與設計

3異步串行通訊控制器的結構設計

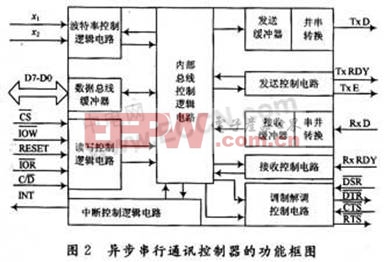

異步串行通訊控制器的內部結構可分為控制邏輯電路和寄存器組兩大部分。在控制邏輯電路中,包括波特率控制電路、讀寫控制邏輯電路、發送控制電路、接收控制電路、調制解調器控制邏輯電路、中斷控制邏輯電路和內部總線控制邏輯電路。寄存器組分為模式寄存器、控制寄存器和狀態寄存器。結構框圖如圖2所示。

該異步串行通訊控制器提供的模式寄存器和控制寄存器,用來設定奇偶校驗、傳輸速率、握手機制以及中斷。在這個設計中,提供了3種奇偶校驗選擇:不采用、奇校驗或偶校驗。傳輸速率的設定是通過向模式寄存器中設置特定的數值,來選擇波特率因子,再結合外部連入的時鐘信號就可以得出傳輸的波特率了。它們之間的關系是:時鐘頻率=波特率因子×波特率。

3.1發送數據模塊

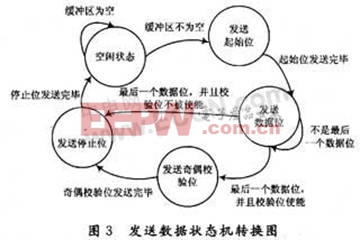

串行異步通信的發送器的實現要比接收器簡單很多。沒有數據要發送時,發送數據寄存器為空,發送器處于空閑狀態;當檢測到發送數據寄存器滿信號后,發送器開始發送起始位,同時8個數據位被并行裝入發送移位寄存器,停止位緊接著數據位指示數據幀結束。只有發送數據寄存器為空時,待發送的數據才能被裝入,在設計中用一個TxE信號來告訴CPU此時控制器的發送寄存器為空。程序中使用計數器來保證發送數據時時鐘的正確。這里使用一個狀態機描述發送過程,圖3是發送器狀態機狀態轉換示意圖。

評論