采用中檔FPGA設計面向PCI Express系統的解決方案

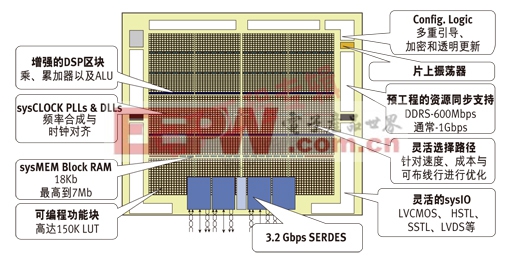

如果采用整合的解決方案,首個挑戰是尋找一個低成本的器件。在過去,PCI Express需要的串行鏈路一般只在高端昂貴的FPGA中才有。然而,今天許多應用需要較低成本的解決方案。中檔LatticeECP2M,或最近推出的LatticeECP3 FPGA系列,擁有適合這種應用的一些功能。這兩種器件都集成了可用于實現PCI Express x1或x4的串行通道。除了低成本優勢外,與高端FPGA解決方案相比,這兩類器件的功耗也非常低。該“節能方案”使系統工程師能夠降低功耗,因此只需要使用較小供電電源。圖3展示了近期推出的ECP3 FPGA系列的結構圖。

圖3:LatticeECP3中檔FPGA框圖,內有集成的SERDES模塊。

利用這些FPGA的另一個優點是它們能夠處理PCI Express使用的擴頻時鐘。許多其他的“單芯片”解決方案推薦使用外部的PLL和去除抖動來處理時鐘,這意味著電路板上會有兩到三個額外的器件。這些器件也可用在工業溫度范圍。

既然這些FPGA的串行鏈路只能實現物理層的SERDES部分,所以需要額外的邏輯來實現完整的PCS。這由軟IP核來完成,它可以配置成x1或x4 PCI Express端點。萊迪思的ispLEVER設計軟件包括一個稱為IPexpress的工具,通過GUI來配置功能,如PLL、存儲器等,還有軟IP。PCI Express核可從萊迪思網站上下載,使用IP Express進行配置并產生編程文件。即使沒有有效許可證,也可以運行這個應用數小時,從而獲得一個全面的系統評估。

為了符合系統的需要,配置PCI Express核的某些功能是非常重要的。例如, PCI Express提供不同的有效載荷大小。有效載荷的規模越大,核中需要的FIFO也越大。為了節約資源,可以通過IPexpress來選擇針對PCI Express核的正確有效載荷的大小。還有一些應加以調整的其他參數,以針對系統要求優化FPGA的利用率。

在許多項目開發中,只有在開發后期才能得到樣機電路板。為了熟悉PCI Express的協議,可從萊迪思獲取PCI Express設計套件。該套件包含了電路板,可用于x1或x4的插槽,并有一些演示配置:

* 基本方法

o 用戶訪問內存和寄存器

o 在電腦上運行演示與在電路板上的PCIe IP核之間提供簡單的互動

* 吞吐量

o 在PCIe核和SERDES之間演示和測量帶寬性能

* Scatter Gather DMA

o 使用DMA在PC機內存和PCI Express卡之間傳送數據

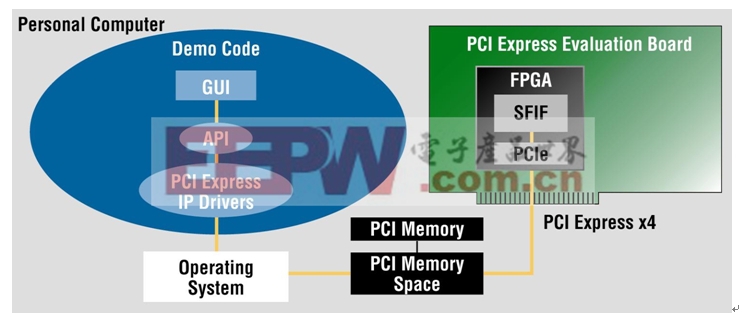

設計人員可以選擇使用其中一個準備好的編程文件,在30分鐘內構建一個完整的演示。套件不僅提供了硬件設計文件,而且還提供驅動程序和運行在PC上的應用程序,這樣就為設計人員的應用提供了一個良好的起點。圖4展示了萊迪思的一個完整的PCI Express演示設計。

圖4:Lattice PCI Express的演示。

用協議分析儀和示波器可以調試系統。但是,利用功能或者RTL級仿真時,設計人員已經可以找到許多問題。

系統調試的三個主要方法:

* 串行環回

* 激勵發生器和測試器

* 總線功能模型

萊迪思的PCI Express核包含一個簡單的采用串行環回的測試平臺。借助一些來自測試平臺的互動建立PCI Express鏈路,并發送一些數據包。這是仿真設計的非常基本的方法。

一個更先進的方法是使用激勵發生器和測試器。FPGA中串行鏈路的仿真模型被一個模型所取代,后者生成數據包,并檢查FPGA內的邏輯響應。

最全面且成本昂貴的方法是建立總線功能模型。有幾個供應商提供PCI Express的仿真模型。根據總線功能模型,設計人員可以測試應用程序,以及FPGA的串行鏈路與整個系統的互動。

評論