基于FPGA的智能誤碼測試儀

1.3 誤碼儀基本測試過程

m序列發生模塊首先根據用戶的速率要求發送測試序列。該序列經過被測信道傳輸后到達接收端,并送入位于FPGA內的位同步模塊。位同步模塊恢復碼元時鐘成功后,會將這一時鐘送至其它模塊,并通知單片機位同步成功。其它模塊利用本地時鐘完成檢驗序列恢復、同步及比較,并由此得到誤碼信息:誤碼數和總碼數。該信息實時傳送給單片機后,單片機每隔1秒進行一次誤碼率的計算,并將具體日期、時間和誤碼率大小顯示在LCD上。如果誤碼率大于0則認為發生了一次誤碼事件,單片機會將此事件發生的時間和誤碼率的大小記錄在儲存器內,并通過RS232串口上傳至PC機。

2 核心部分設計

FPGA中的位同步模塊和序列同步模塊是實現誤碼儀的關鍵。這兩個模塊設計得好壞直接影響著誤碼儀的整體性能。同時,誤碼儀智能能力的實現也離不開單片機的有效工作。

2.1 位同步模塊

實際應用中,由于不同的被測信道采用不同的技術,因此其傳輸方式、傳輸速率、復雜程度都各不相同。這就要求誤碼儀中的位同步模塊具有較強的適應能力。一般常見的同步方法如插入導頻法、濾波法等都無法滿足信道多變的要求5。為此,根據數字鎖相環的基本原理并結合FPGA的結構特點,研究了一種自適應的智能鎖相算法,該算法可使誤碼儀在較寬的速率范圍內對信號時鐘進行智能提取和跟蹤,具有較高的實用價值。

圖2是該位同步模塊的結構框圖。為了使接收端能快速、準確地提取碼元時鐘,發送端在發送m序列前應先發送一定數量的0101序列(見圖3中的S1),其中“0”和“1”的寬度與單個碼元寬度相同。在接收端預先不知道信號單個碼元寬度(即碼元時鐘)的情況下,位同步模塊首先進行碼元寬度檢測。這一工作主要由碼元寬度計數器完成。該計數器在高速全局時鐘驅動下分別對信號中的“0”、“1”電平進行寬度計數。

由于發送的是0101序列,因此碼元寬度計數器的計數值N將保持在一定閾值范圍內,這一N值表示了發來信號碼元寬度相當于N個全局時鐘寬度。由此,位同步模塊便獲得了發來信號的單個碼元寬度信息。之后,位同步模塊在傳輸信號的上升沿或下降沿啟動本地N計數器,產生與發端信號同頻的本地時鐘S2。S2經過一個定值延時器延時Nx個全局時鐘寬度后,得到信號S3。S3與S1在鑒相器中進行異或門鑒相,其結果為S4。由圖3可見,若S4中高電平寬度等于Nx個全局時鐘寬度,則本地時鐘S2與發端時鐘S1同相。若S4中高電平寬度大于Nx,則本地時鐘滯后,反之則超前。由此得到了本地時鐘超前或滯后的信息。控制器根據這一信息對本地N計數器進行加、扣脈沖操作,使得本地時鐘與發端時鐘保持同相。

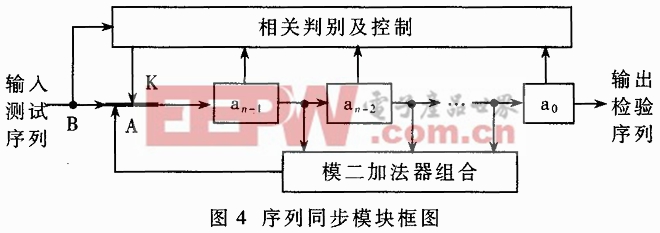

圖4 序列同步模塊框圖

在m序列中,連0、連1的情況很多,為了防止鑒相器在此期間誤操作,設計了判別及控制電路,在信號出現連0或連1時使鑒相器不操作,讓本地N計數器始終以N為計數值計數。采用這種同步方法后,不僅誤碼儀同步適應范圍加寬,而且本地恢復時鐘的精度也僅與全局時鐘有關,而與發端信號速率無關。實際測試證實,在信號存在50個連0時,位同步模塊仍能正常工作。

2.2 序列同步模塊

前面已經提到,m序列是周期序列,測試序列和檢驗序列的比較應以周期內的同一位置作為起點。因此,在序列比較前應首先進行序列同步。常見的序列同步方法有:滑動相關捕捉法、序列相關捕捉法、SAW器件捕捉法等6。這些方法都是利用序列的相關特性進行同步的,存在著結構復雜、同步時間較長等缺陷,不適合用FPGA實現。為了使誤碼儀能在不知道發送端序列發生器初始狀態的情況下進行快速盲同步,在實際設計中采用了開關門m序列同步算法7。其原理框圖如圖4所示。

在初始狀態下,開關K置于B位置,發端送來的測試序列在完成位同步后移位送入寄存器an-1…a0。存滿后,開關K置于A位置。寄存器an-1…a0和模二加法器在本地時鐘的驅動下產生出檢驗序列。由于m序列的下一存儲器狀態組合僅取決于當前的狀態組合,因此,如果最初的9個接收碼元是正確的,則隨后產生的所有碼元都是與測試序列相同和同步的。之后,測試序列與檢驗序列需要進行一次相關比較,如在若干個(如5個)碼元周期內其相關值超過閾值,則可認為兩序列同步,否則需要重新進行同步操作。

采用這一方法后,序列同步時間大大縮短,有利于進行快速測試。

評論