基于CPLD的光伏逆變器鎖相及保護電路設計

0 引言

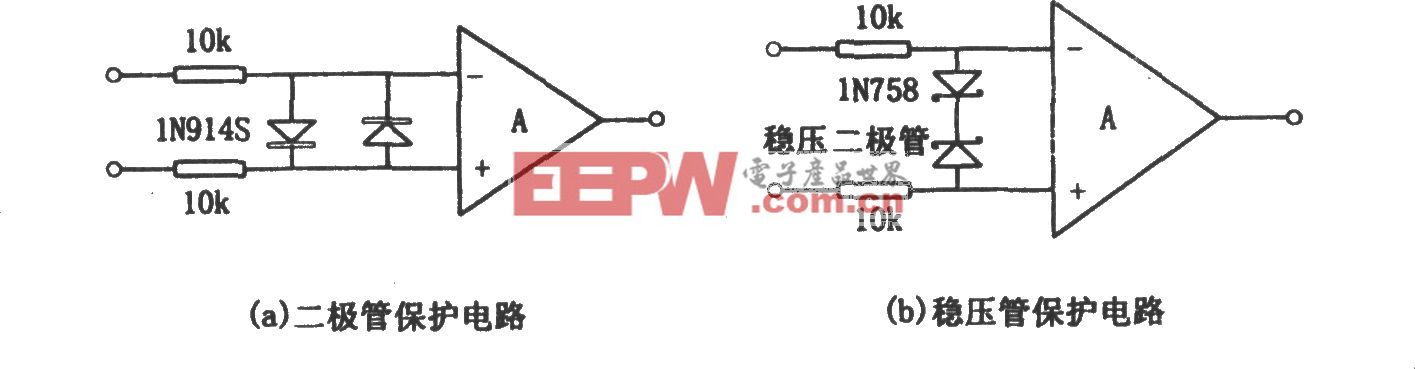

在光伏并網系統的逆變器電路中,對電網電壓的鎖相是一項關鍵技術。由于電力系統在工作時會產生較大的電磁干擾,因此,其簡單的鎖相方法很容易受到干擾而失鎖,從而導致系統無法正常運行。在這種情況下,設計采用對電網電壓進行過零檢測后再將信號送人CPLD,然后由CPLD實現對電網電壓進行數字鎖相的方法,可以有效地防止相位因干擾而發生抖動或者失鎖的現象,保證系統的正常運行。另外,本系統還使用CPLD對DSP產生的PWM波控制信號和系統運行時的各項參數進行監控,一旦發現異常,立即使系統停機,并通知DSP發生異常,從而實現了對系統的硬件保護。

1 系統整體結構組成

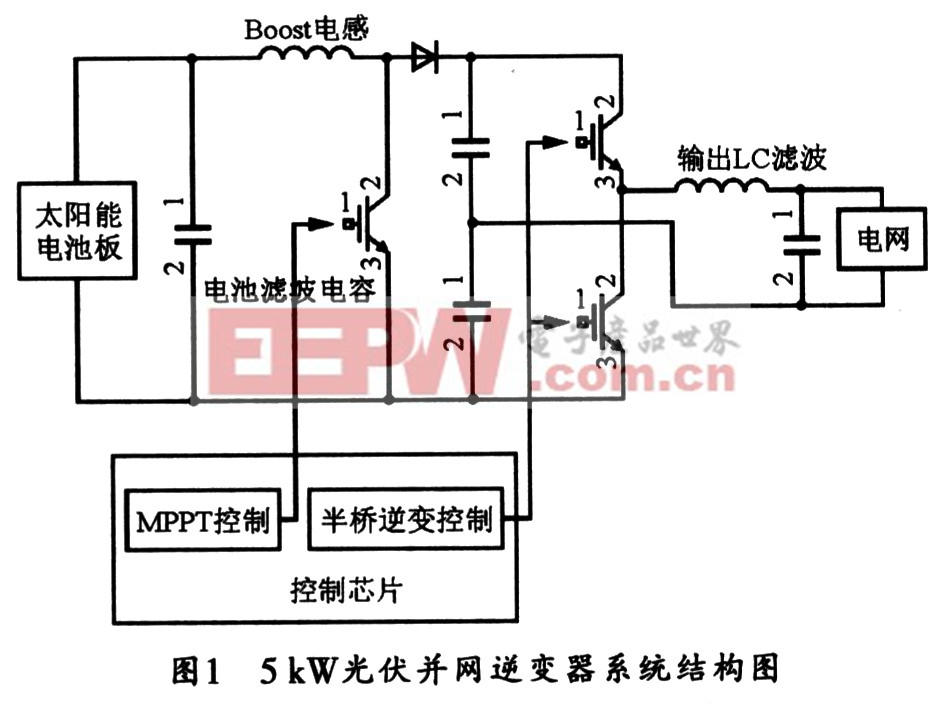

本文所介紹的設計方法是5 kW光伏并網發電系統中逆變器的一部分,該光伏并網逆變器可實現額定功率為5 kW的太陽能電池陣列的最大功率跟蹤與并網輸出。其逆變器的系統結構圖如圖1所示。

本控制系統由TI DSP2812作為主控芯片,Xilinx CPLD XC9572XL用作數字鎖相與保護電路,XC9572XL為3.3 V內核電壓的CPLD,它由4個54V18功能模塊組成,可提供1600個5 ns延遲可用門。

2 數字鎖相電路的設計與實現

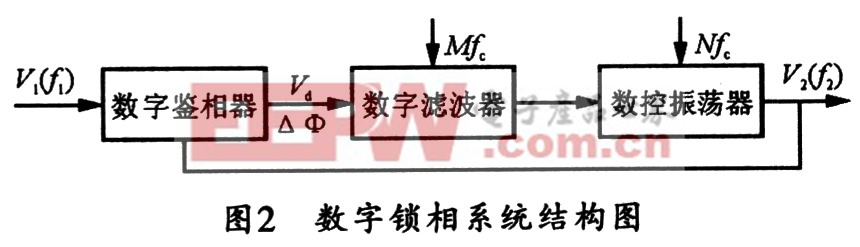

數字鎖相電路的系統結構圖如圖2所示。該電路由數字鑒相器、數字濾波器和數控振蕩器組成。

如果把圖2所示的數字鎖相電路中的數字濾波器看成一個分頻器,則其分頻比為Mfc/K,此時的輸出頻率為:

f'=K'△φMfc/K

其中,△φ為輸入信號V1與輸出信號V2的相位差;fc為環路的中心頻率。那么,該數控振蕩器的輸出頻率為:

f2=f1+K'△φMfc(kN)

由于鎖定的極限范圍為K'△φ=±1,所以,可得到環路的捕捉帶:

△fmax=f2max-f1=Mfc(kN)

這樣,當環路鎖定時,f2=f1其系統穩態相位誤差為:

△φ(∞)=NK(f2-f1)/(k'Mfc)

可見,只要合理選擇K值,就能使輸出信號V2的相位較好地跟蹤輸入V1的相位,從而達到鎖定之目的。如果K值選的太大,環路捕捉帶就會變小,這將導致捕捉時間增大;而如果K直太小,則可能會出現頻繁進位,借位脈沖。從而使相位出現抖動。

評論