基于FPGA嵌入式的多比特自相關(guān)器設計

從表1中可以看出:在存儲器中存儲的N個數(shù)值中僅有N-1-k個數(shù)據(jù)進行了自相關(guān)運算,超出這個范圍的數(shù)據(jù)應視為無效數(shù)據(jù)被舍棄。因此如果N的長度過短或者k的數(shù)值過大,存儲器中的數(shù)據(jù)將有相當一部分數(shù)據(jù)被舍棄,并且隨著k值的增加被舍棄的數(shù)據(jù)量將在整個存儲數(shù)據(jù)量中的比例越來越大;但是由于信號的自相關(guān)性隨著延遲k增加而降低,在做自相關(guān)運算時一般采用較小的k值。為此,如果采用較大的RAM存儲器和較小的k值,在一組存儲數(shù)據(jù)中舍棄的數(shù)據(jù)其實是占比例很小的。例如在k=3的情況下,即延時為3個A/D轉(zhuǎn)換周期,CyclmleⅡFPGA中存儲器的最大存儲長度為65 536個8 b存儲單元,舍棄記錄數(shù)據(jù)為3個8 b,舍棄數(shù)據(jù)量僅占存儲數(shù)據(jù)量的0.004%,在自相關(guān)處理時是能夠接受的。如圖6所示。

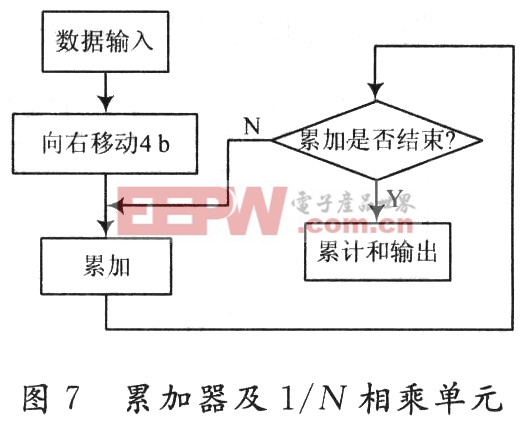

2.2 累加器及1/N相乘單元實現(xiàn):

如果使用2的N階次冪數(shù)據(jù)用作自相關(guān)計算,在二進制下可以通過向右移位N個bit位實現(xiàn)除法功能。在設計中采用了2×16個采樣數(shù)據(jù)組成的數(shù)組完成自相關(guān)計算,其算法具體流程圖如圖7所示。

3 微處理器的設計實現(xiàn)

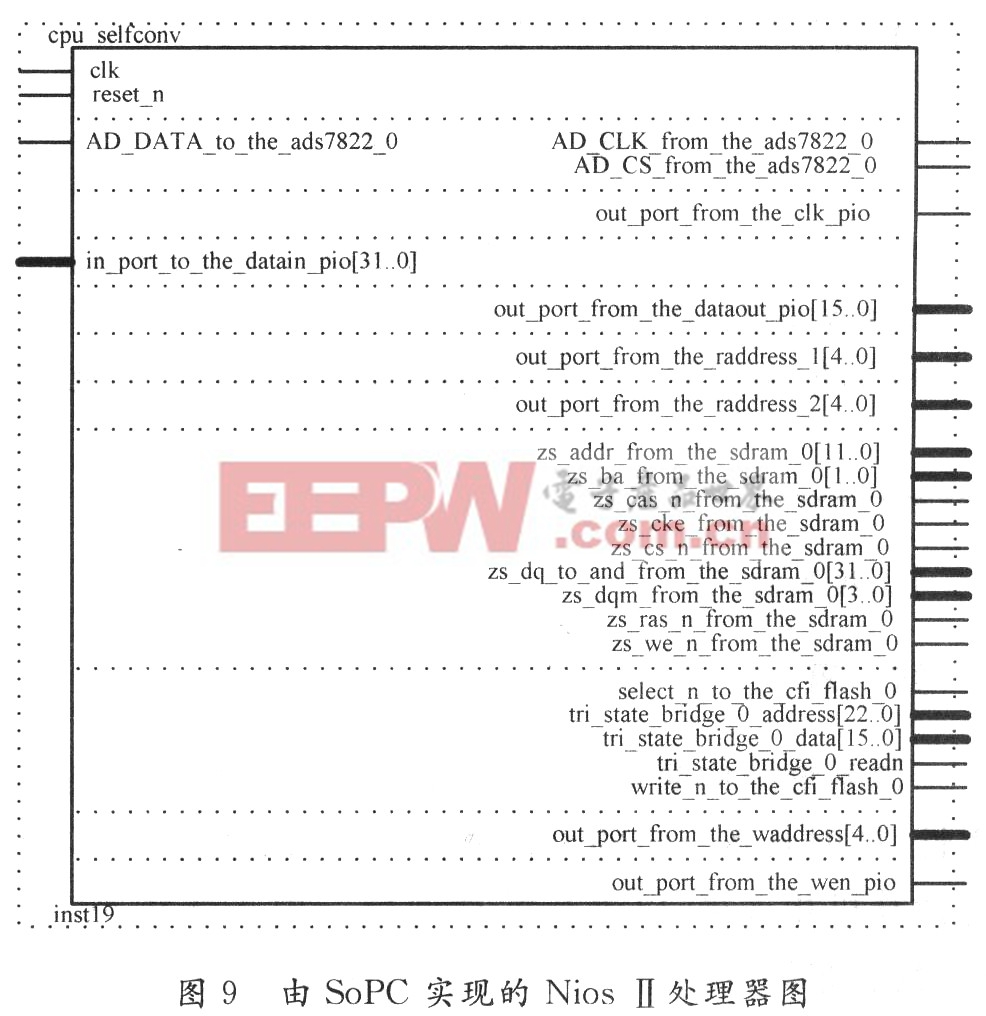

嵌入式微處理器的設計包括3個部分:利用SoPCBuilder定制的軟核CPU,在Quartus II環(huán)境下設計的電路和Nios II編程。

Nios II的軟件編程主要基于嵌入式操作系統(tǒng)μC/OS-Ⅱ。μC/OS-Ⅱ是一個完整的、可移植、固化和剪裁的占先式實時多任務核(Kernel)。從1992年發(fā)布至今,μC/OS-II已經(jīng)有上百個的商業(yè)應用案例,在40多種處理器上成功移植。其中Altera提供對μC/OS-II的完整支持,非常容易使用。

μC/OS―II提供以下系統(tǒng)服務:任務管理(Task Management);事件標志(Event Flag);消息傳遞(Mes-sage Passing);內(nèi)存管理(Memory Management);信號量(Semaphores);時間管理(Time Management)。在應用程序中,用戶可以方便地使用這些系統(tǒng)調(diào)用實現(xiàn)目標功能。

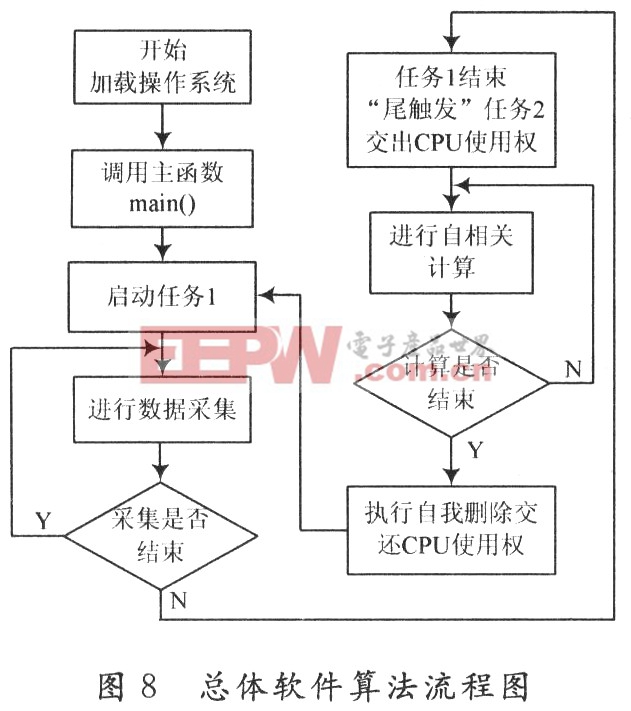

在該設計中,建立了一個主任務和兩個子任務(任務1,任務2):主任務主要是負責啟動子任務;任務1主要負責數(shù)據(jù)的采集和采集數(shù)據(jù)的存儲,任務2主要負責調(diào)用存儲器中存儲的采集數(shù)據(jù)控制外圍計算模塊進行自相關(guān)計算。總體軟件算法流程圖如圖8所示。圖9為由SoPC實現(xiàn)的Nios II處理器圖。

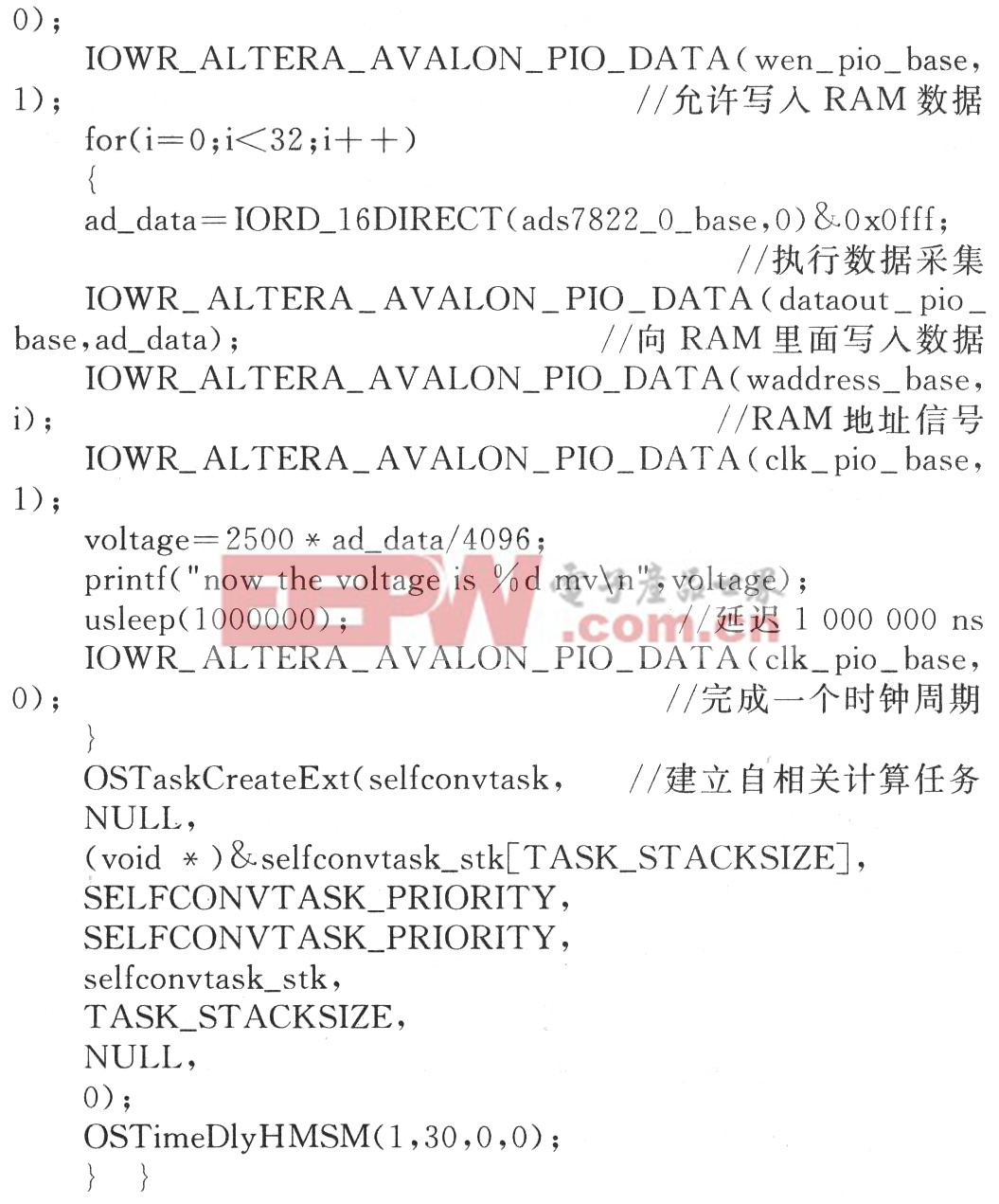

在Nios II系統(tǒng)中,首先,通過main()主函數(shù)調(diào)用OSTaskCreateExt()函數(shù)創(chuàng)建任務1,即數(shù)據(jù)采集任務。

由于AD7822作為AVALON的從外設掛接在了AVALON總線上,通過在任務1中通過調(diào)用IORD_16DIRECT()端口查詢函數(shù)實時發(fā)起A從端口傳輸啟動AD7822,獲取采集數(shù)據(jù),然后使能外圍RAM的wren端口存儲。當存儲到該設計中存儲器長度的數(shù)據(jù)以后,通過“尾觸發(fā)”方式啟動任務2,即自相關(guān)計算任務,并且調(diào)用延遲函數(shù)OSTimeDlyHMSM(),交出CPU的使用權(quán)。程序要點如下:

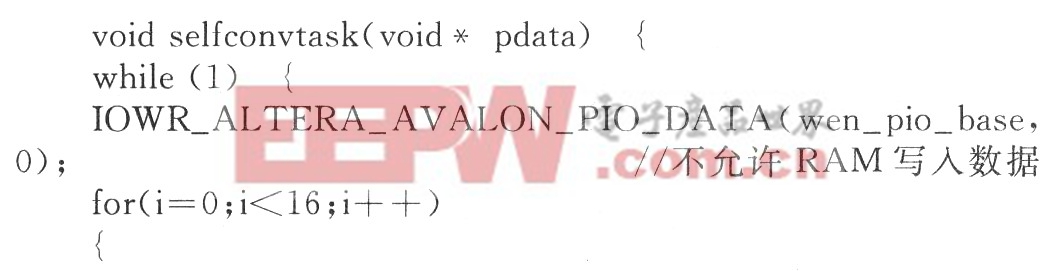

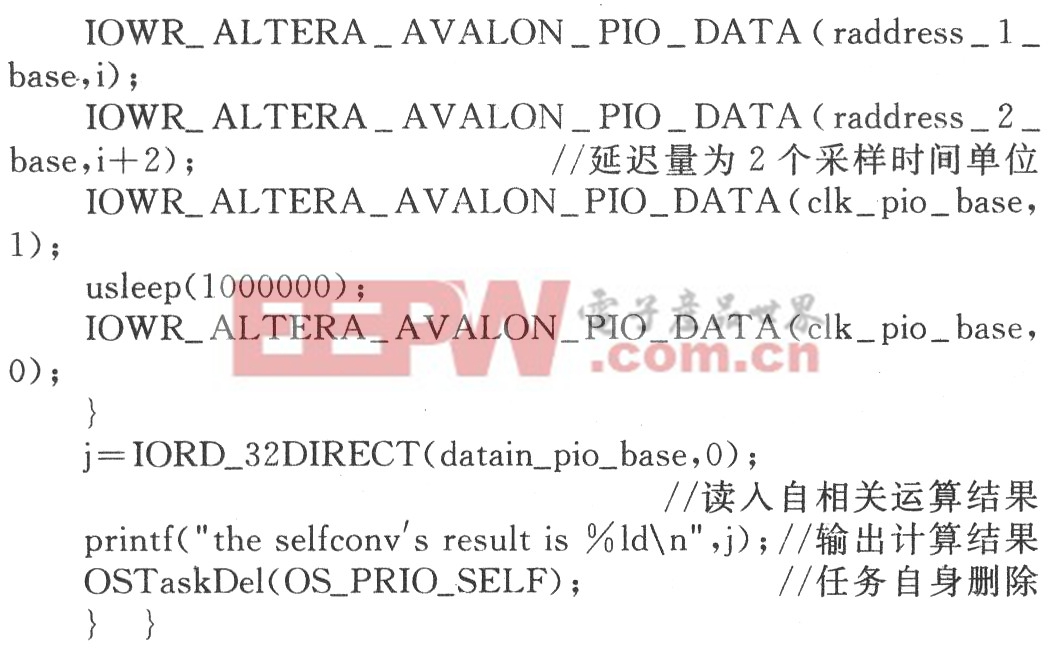

在任務2中,首先關(guān)閉兩個存儲器的寫入使能,使之只能讀出數(shù)據(jù);然后輸出相應的兩個地址碼:兩個地址碼之間有相對k的延時,并且同時使能18×18乘法器,累加器及1/N相乘單元,當循環(huán)完成后,自動刪除任務2,交CPU使用權(quán)給數(shù)據(jù)采集任務。程序要點如下:

4 結(jié) 語

首先,該設計采用嵌入式操作系統(tǒng)實時控制外圍運算邏輯電路的方式。實現(xiàn)了多乘加的DSP運算,由于嵌入式操作系統(tǒng)的靈活性和廣泛的可移植性,使得該設計的可讀性和移植性增強;其次,本設計采用天生并行結(jié)構(gòu)的FPGA處理器完成多乘加運算,有利于提高運算速度和處理的穩(wěn)定度;再次,將必要的外設作為AVALON總線器件,采用總線查詢傳輸?shù)姆绞竭M行訪問,不必在嵌入式操作系統(tǒng)中過多的考慮底層硬件的驅(qū)動和時序,這樣提高電路的穩(wěn)定性且也增強了程序的通用性。

評論