用FPGA技術實現模擬雷達信號

3控制芯片VHDL語言描述

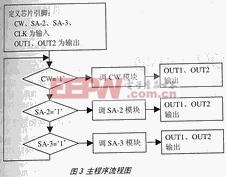

由芯片的結構可以看出,6個分頻器電路除了它們的分頻系數不同外,VHDL(甚高速集成電路描述語言)的結構是類似的,稍加改變便可設計成各自獨立的元件單元。脈寬整形電路可設計成標準的基本單元,以元件形成供4個脈寬整形電路和消抖動電路調用。SA-2指令組形成電路、編碼器和選擇器分別設計成獨立的元件單元。將上述各單元按它們的信號關系連接起來,便構成了芯片構造體描述。該設計直接采用VHDL的RTL(寄存器傳輸描述)方式,來簡化設計步驟和縮短設計時間。其VHDL硬件描述語言主程序流程圖如圖3所示。

結束語

我們采用VHDL硬件描述語言,通過MAX+PLUS Ⅱ開發平臺,經編譯、仿真無誤后,寫入Altera公司EPM7064S器件中,經調試,其性能完全達到設計要求。

評論