基于FPGA的脈沖壓縮仿真與實現

3 邏輯設計和仿真

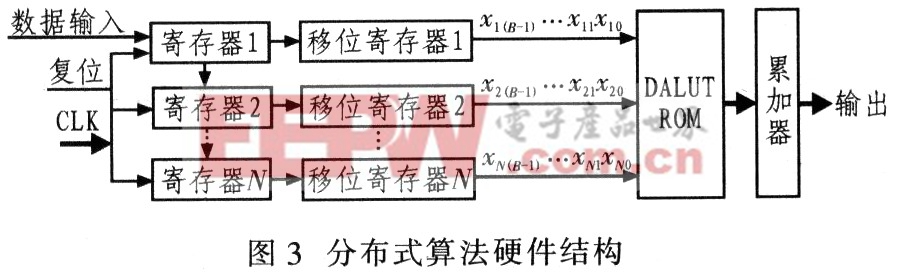

3.1 分布式算法的硬件結構

根據分布式算法原理得出采用FPGA實現的分布式算法的硬件結構,如圖3所示。本文引用地址:http://cqxgywz.com/article/192017.htm

圖3中N為該模塊的濾波器階數,那么DALUT有2N個存儲單元,如果濾波器抽頭數過多,查找表規模隨抽頭數的增加成指數遞增。因此實現高階濾波器時,要分割查找表。因為卷積運算是線性的,所以在將每個子表的輸出相加可得到總輸出。邏輯設計是基于Altera公司的Stratix系列FPGA為平臺,在OuartusII軟件中利用VHDL語言和原理圖進行邏輯設計。

3.2 5階FIR濾波器設計

Stratix器件的LPM_ROM模塊最少有32(25)個存儲單元,所以設定濾波器模塊階數N=5。5階濾波器模塊設計如圖4所示,其中lpm_dff0為12位鎖存器,5個鎖存器對輸入數據進行移位寄存,firda5為分布式算法模塊,DATAS[11:0]輸出引腳是濾波器模塊最后一個鎖存器輸出,作為濾波器模塊級聯時不同濾波器模塊之間的數據移位。

分布式算法模塊firda5實現數據的并串轉換、DALUT查表、加權累加。設計中采用狀態機實現分布式算法的狀態轉移,這樣簡化計算過程,在實現算法時發揮關鍵作用。根據分布式算法的狀態轉移關系,每輸入一個數據,在下一個數據輸入之前,需要在狀態s1停留12位數據寬度的時鐘時間和2個寄存的時鐘時間(在QuartusII軟件中,器件選用Stratix系列,利用LPM_ROM模塊,地址輸入是寄存輸入,數據輸出也包含寄存器)以及一個數據輸出時鐘時間:所以系統時鐘必須為數據時鐘的16倍,圖中div 16實現16分頻。

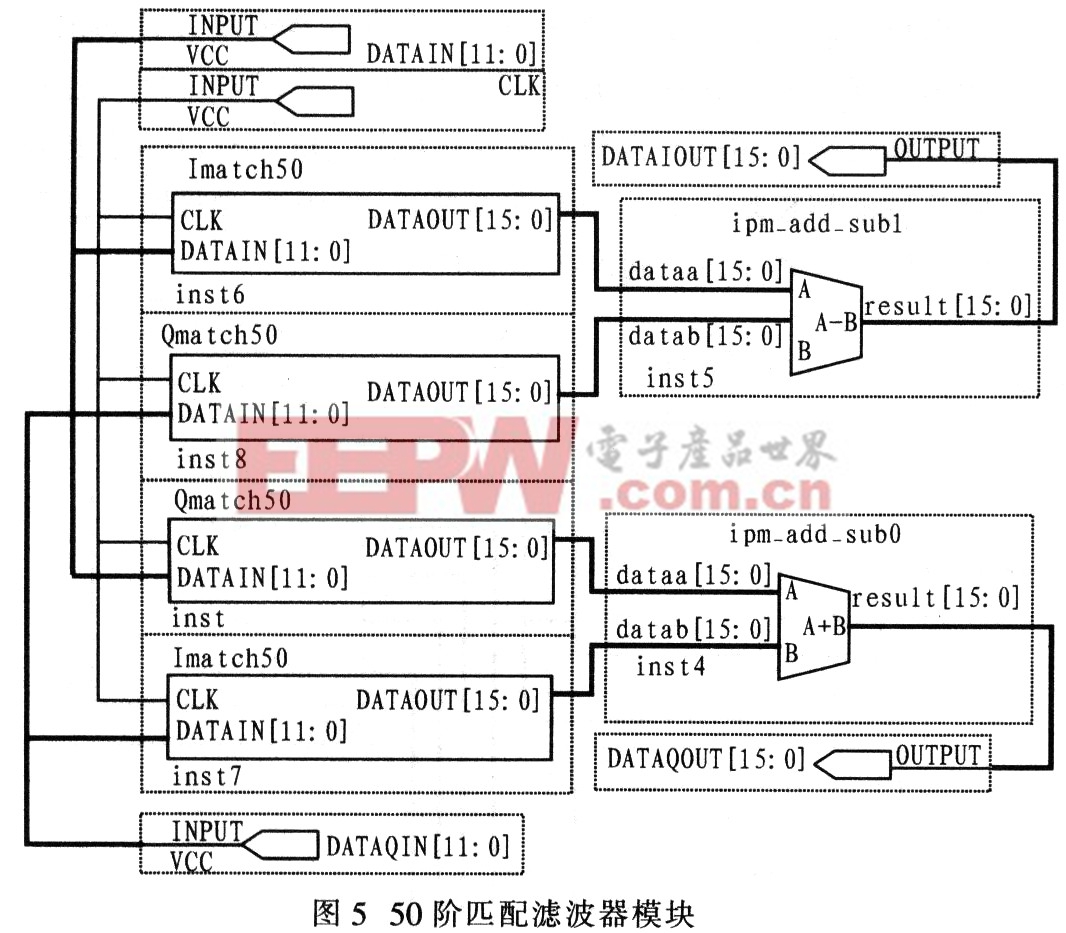

3.3 50階匹配濾波器設計

由于匹配濾波器就是有限脈沖響應(FIR)濾波器,具有線性特性,所以通過低階濾波器的直接級聯相加就可以實現高階濾波器,前一個濾波器的移位數據DATAS[11:0]作為下一個濾波器模塊的信號輸入,每個濾波器模塊都根據圖4設計,只需要根據不同的系數更改DALUT表中的數據。50階匹配濾波器的邏輯設計如圖5所示。其中,Imatch50模塊為匹配濾波器復系數實部對應的50階濾波器,而Qmatch50模塊為匹配濾波器復系數虛部對應的50階濾波器。輸出信號包括16位I信號和16位O信號。

評論