基于FPGA的音頻編解碼芯片接口設計

3.2.2 控制字轉換單元

當START控制位置‘1’時,將控制字寄存器中的數據串行發送給WM8731,當傳輸出現錯誤時,將狀態寄存器中的ACK位置1。如圖6所示。

3.2.3 數字音頻接口單元

當讀入數字音頻標志位C1為‘1’,接收WM873l芯片傳來的數字音頻數據并將其存入外部雙口RAM中,當輸出數字音頻數據標志位C2為‘1’時,將雙口RAM中的音頻數據發送給wM8731。如圖7所示。

3.3 系統仿真

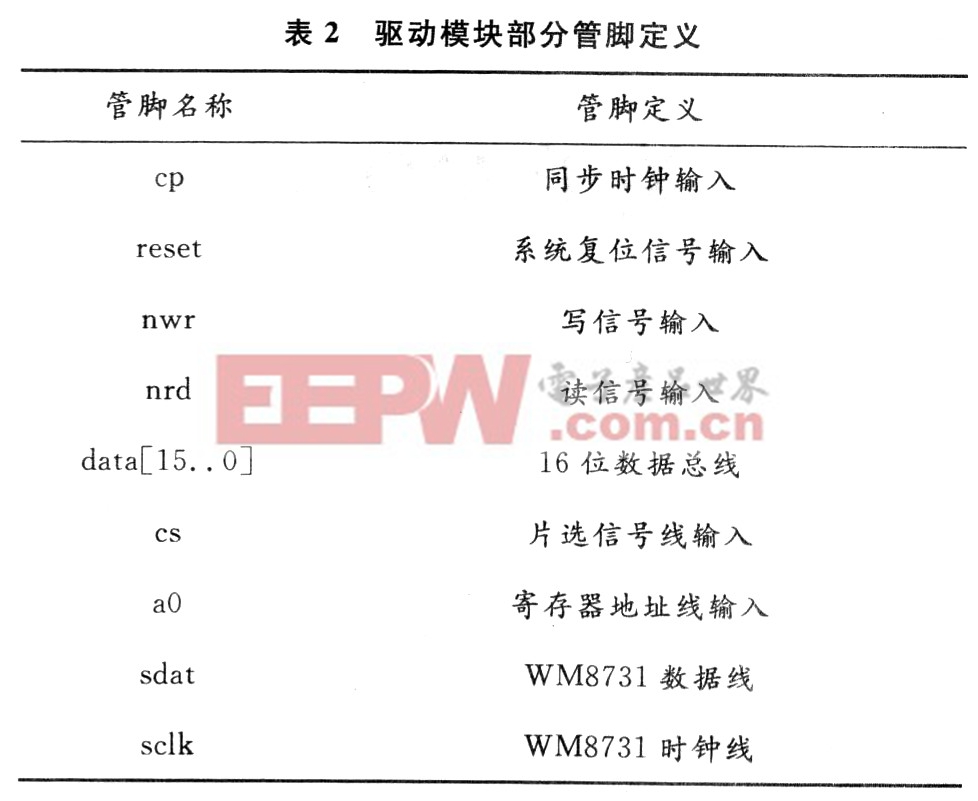

下面給出控制器通過該驅動模塊對WM8731寫控制字的時序仿真如圖8所示。圖中各引腳定義如表2所示。

4 結 語

利用FPGA對音頻編解碼芯片WM8731進行接口電路的設計,實現了控制接口與數字音頻接口的統一控制,簡化了對音頻編解碼芯片WM8731的使用步驟,具有擴展性好、使用簡單方便、易于升級等優點,對其他芯片的接口設計也有一定的參考意義。

評論