基于Matlab和FPGA的FIR數字濾波器設計及實現

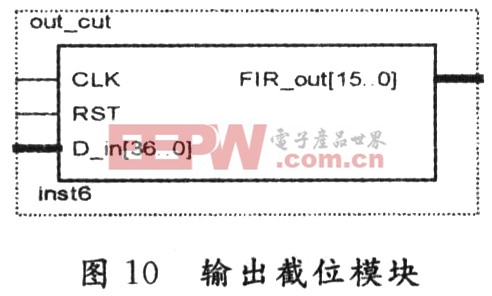

截位是濾波器設計的關鍵,此處的處理方法是:14位的輸入數據(14 b的ADC),18位二進制補碼表示的濾波器系數,除去符號位,相乘后小數位是13+17=30,加法運算不改變小數位數。另外系統測試電路板用的是USB總線,USB控制器的數據位寬是16,因而把輸出數據截到16位,然后送給FIFO,從而傳到計算機。截位用VerilogHDL實現的語句是:

assign FIR_out={D_temp[36],D_temp[29:15]};

此模塊的原理圖如圖10所示,其中FIR_out[15..O]是濾波器的最終輸出。本文引用地址:http://cqxgywz.com/article/192109.htm

在QuarltusⅡ7.0里調用仿真無誤的模塊,組成整個系統,最后仿真無誤后進行系統的實際數據測試。

5 實際測試

測試電路是一基于FPGA和USB的數據采集及處理系統。其原理框圖如圖1l所示。

測試時把一被干擾的模擬信號輸入ADC,采樣得到的數據經過FPGA和USB傳輸到計算機上,然后用Mat―lab顯示出其時域和頻域圖形。

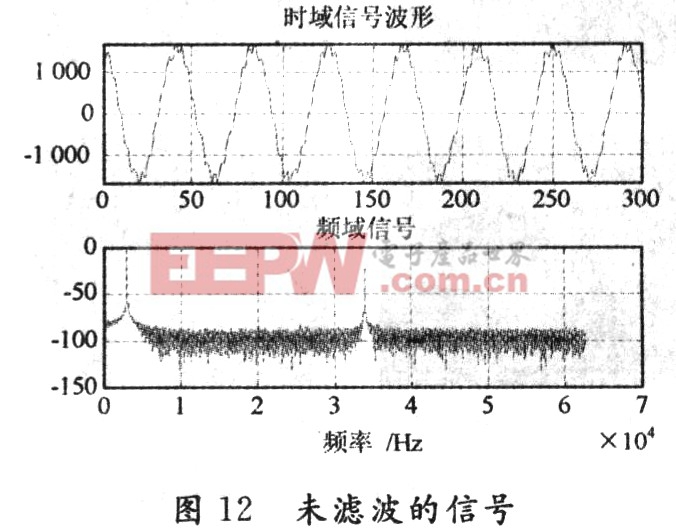

5.1 未濾波時信號波形

輸入信號頻率是3 kHz,含頻率為34 kHz的干擾信號(用兩個信號源合成),下載的FPGA控制程序不含數字濾波器模塊,采樣得到的數據經USB傳到計算機,然后用Matlab顯示出的波形如圖12所示,可以看出干擾信號的相對功率約為一20 dB。

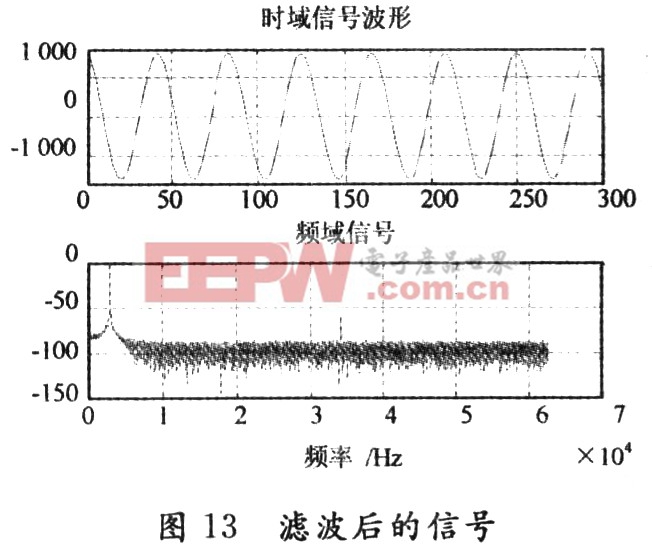

5. 2 濾波后信號波形

把濾波器程序下載到FPGA,輸入信號不變。濾波后波形如圖13所示。

前后對比可以發現,濾波后信號明顯變好,34 kHz的干擾被抑制到約一55 dB,驗證了設計的正確性。

6 結 語

本文給出了用CycloneⅡ系列FPGA實現FIR低通濾波器的設計實例。然后將濾波前后的AD實際采樣數據用Madab顯示出來并做比較,測試結果證明所設計的FIR數字濾波器功能正確,性能良好。并且該數字濾波器有很高的靈活性,濾波器系數在一個表格內,修改其參數即可分別實現低通、高通、帶通等類型。文中所討論的設計方法和實現技術對數字信號處理系統的設計與實現具有重要的實用價值。

評論