無線基站中的FPGA和DSP組合

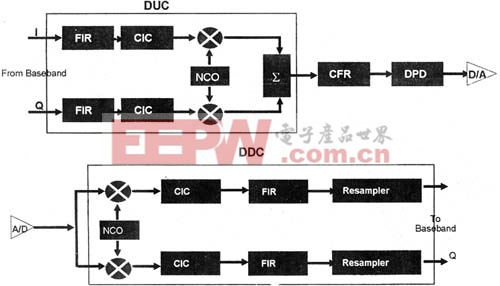

需要CFR和DPD功能來改善用在基站中放大器效率。這些功能也有助于大大降低RF板的總成本。CFR和DPD包含復雜的乘法,取樣率可高達100MSPS以上。類似于DUC,在接收端需要數字下變頻(DDC)把IF頻率變為基頻。DUC和DDC都采用復雜的濾波器結構,包括有限脈沖響應(FIR)和級聯積分梳狀(CIC)濾波器。先進的FPGA提供運行速度高達350MHz的數百個18×18乘法器。這不僅提供并行處理多信道的平臺,而且也是一個經濟集成單芯片方案。

有效的設計方法

隨著標準的穩定,對基站靈活性的要求將降低,而成本變為一個主要的成功因素。選擇FPGA將會大大地節省成本。

混合FPGA/DSP基平臺,為無線基站提供一種有效的設計方法。產品成功的關鍵是根據系統吞吐量要求和成本考慮在FPGA和DSP之間進行合理分配。這將保證產品最終不僅僅只是可縮放的和經濟的,而且靈活、可配置適合多個標準。(彭京湘)

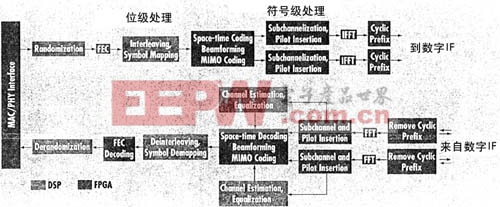

圖1 OFDMA系統中DSP/FPGA分配

圖2 FPGA中的嵌入式DSP單元

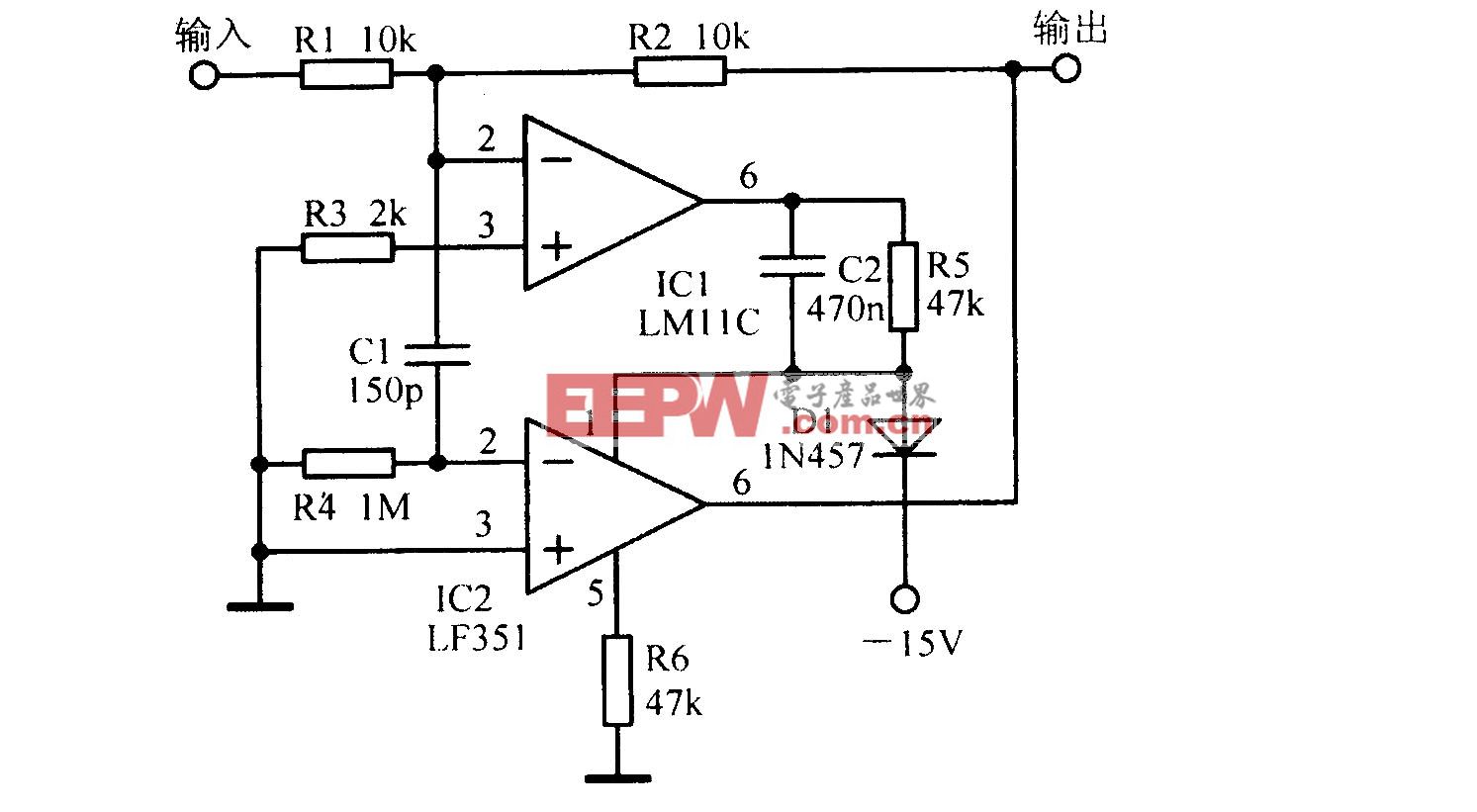

圖3 數字RF處理功能

評論