用內部邏輯分析儀調試FPGA

復雜調試的一個例子是在SMPTE SDI HD顯示中尋找一個特別的像素。在特殊的情況下,找到EAV (end active video)時序是必須的,然后尋找與數據相關的特別線數,再尋找SAV (start active video)時序。最后根據線中對應的像素,計算字節數目,參見圖2。

圖2 SDI HD數據流實例

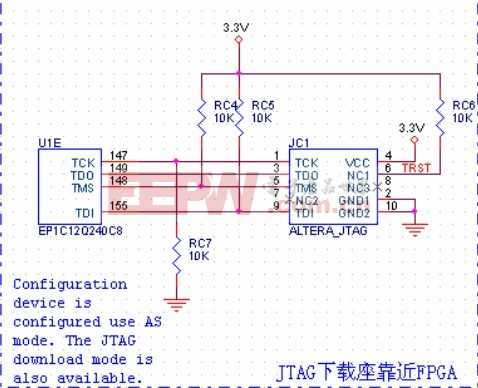

為了調試找到這種數據需要尋找值的時序,再找特殊值,然后結束序列,最后在捕獲數據前數時鐘的數目。為了理解是如何做的,必須查看具體的實現過程。萊迪思的Reveal硬件調試器使用觸發單元和觸發表示以決定觸發點。觸發單元是一個比較器,觸發表示允許觸發單元和序列值組合在一起。

對于這個SDI實例,用3個觸發單元來定義EAV和SAV序列,另外的觸發單元用于線數,最后在發現數據前的一個計數聲明用于等待。觸發建立的實例如圖3所示。這個設置可以用來尋找任何要求的線數和像素,因為線數觸發的值和計數可以動態地改變。

圖3 觸發設置的實例

結論

工程師將繼續使用外部邏輯分析儀,因為用它分析系統級功能時是很有價值的。但是用于內部FPGA調試需要連接到電路板,信號的數目受到了限制。而內部邏輯分析儀在可用信號數目方面提供了很大的自由度,但是在觸發邏輯和跟蹤存儲器方面受到約束。然而小心地使用觸發選項使內部邏輯分析儀在精確的時間開始捕獲數據,要最大化可用的資源。這個例子中,需要分析在SDI視頻信號里特殊的像素(線和字)的復雜實現被分解成簡單的元素,這種方法提高了效率。這個例子只是瀏覽了內部邏輯分析儀的使用和應用。由于FPGA設計復雜性不斷增加,針對功能驗證和調試,內部邏輯分析儀和類似的工具受到了設計者的青睞

評論