芯片設計中的功耗估計與優化技術

3.2估算的流程

因為指令與行為級估算的精確度太差,電路級估算的耗時過多,所以在業界的實踐中采用較少。RTL與gate級估算是常用的選擇。實際功耗分析的執行必須借助工具的輔助,目前業界通常的選擇是在RTL級采用power compiler,在門級采用primepower。

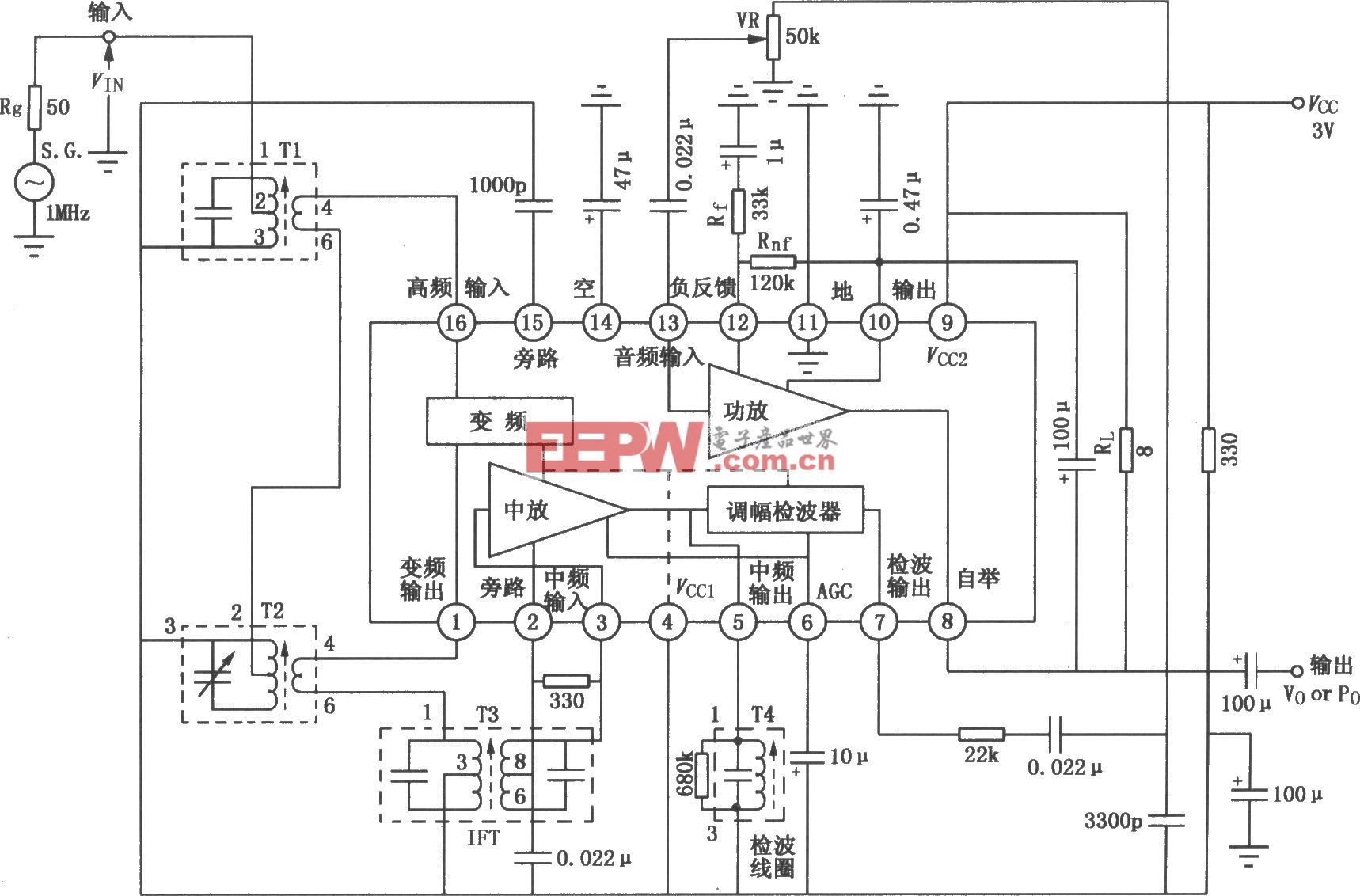

圖2

下面以power compiler為例,說明門級估算的步驟。

在dc compile前,設置下面的變量:

power_preserve_rtl_hier_names = false/true

編譯

寫出ddc文件

仿真生成vcd 文件

vcd2saif轉化為.saif文件 (注意vcd2saif由csh調用,而不是在dc_shell界面調用)

讀入ddc網表

read_saif

report_power

4 功耗的優化

4.1優化的原則

圖3是幾個典型設計中功耗分布數據:

(數據來自“International Solid-State Circuits Conference”)

圖3

我們的目標是減少時鐘樹、標準單元和存儲器的功耗。功耗與性能通常是充滿矛盾的:

1)使時鐘變慢(更少的轉換),但我們想要更快的處理速度。

2)減小Vdd,但Vdd變小會限制時鐘速度。

3)更少的電路,但更多的晶體管可以做更多的工作。

簡言之,我們想用最少的能量完成最大量的任務。實現方式是對電路動作的控制精細化,僅讓恰好需要的電路,在需要的時間內動作,而不浪費分毫。完成這一任務,需要設計者有效率地管理電路的動作。

現代系統是如此復雜,以致設計者必須切分為若干層次,分步前行才能把握:

軟件 -> 架構 -> 邏輯 -> 電路

每一層次中,設計者對電路動作的控制范圍和手段都是不同的。軟件是硬件動作的總調度師,設計者可以根據特定應用,關掉整個模塊或減少無效的動作。進入架構層,視角轉為怎樣將設定任務合理分配到各個模塊,協調動作最有效率,如pipeline、分布式計算、并行計算等。在邏輯層,則考慮怎樣實現一步動作僅使需要的電路動作。電路層的視角更為精細,通過調節平衡信號到達時間,驅動單元大小等手段,使電路的動作耗能最小。這里存在一個重要規律,稱作效率遞減率:

在高的抽象層次減少功耗的效率會比低的層次更高。

所以,降低功耗是一個系統工程,需要軟件、硬件、電路、工藝等人員的共同努力。這里,我們將采用架構與邏輯的視角進行下面的討論。

4.2 架構考慮

1)切分工作模式,硬件要可以提供一個接口,以使軟件可以控制電路模塊的動作與否。不工作的模塊掛起。

2)分布式計算:將整個任務切分到不同模塊,在內部處理高活動性信號。

雖然總計算量沒有改變,但對單個模塊,時間要求降低,可以降頻或降壓。

3)并行計算:相同時間內計算量相同,但可降頻/壓。

(計算量=開關的次數,開關次數沒變,但每次開關的功耗成本降了)

4)pipeline

每步的計算量減少,可以在性能相同的情況下,降低工作頻率。

5)可編程性與hard-wire的權衡

可編程性越強,完成相同的任務耗電越多。

(見參考文獻[7])

圖4

4.3 RAM的功耗優化

很明顯,大的RAM比小的RAM耗電要多,將整塊的RAM分成小塊可以降低存取功耗。

圖5

值得注意的一點是,多數設計者認為片選信號無效,RAM即進入最小功耗。實際上,若此時其數據/地址端口信號有翻轉,會耗費相當的電力(約占激活功耗的20%)。在不存取時,最佳的方式是,保持片選無效,地址、數據是恒定值。

4.4時鐘樹單元/連線

4.4.1 時鐘門控的原理

在典型的數字芯片中,時鐘網絡的功耗可以占到總量的50%,這是一個龐大的數字。一個行之有效的方案是使用時鐘門控,將當前未工作邏輯的時鐘樹關閉。比如下面的邏輯,在EN是0時,可以將右側的register bank的時鐘關閉。

圖6

時鐘門控邏輯加入的方式有兩種:手動和自動。

a) 手動方式

在每個IP模塊的時鐘根節點加入,EN信號可以由程序設定產生。

b) 自動方式

dc_shell > set_clock_gating_style (options) 選擇時鐘門控的方式和條件

dc_shell > analyze -f design.v 讀入設計

dc_shell > elaborate MY_DESIGN 構造設計

dc_shell > insert_clock_gating 將符合條件的邏輯門控

dc_shell > create_clock -period 10 -name CLK 創建時鐘

dc_shell > propagate_constraints -gate_clock 加入時鐘門控單元的時序約束

手動和自動結合的方式可以達到最好的效率。

4.4.2 gating 單元的選擇

a)latch-based(圖7)

圖7

b)latch-free(圖8)

評論