信號完整性分析基礎系列之三--串行數據測試中的CDR

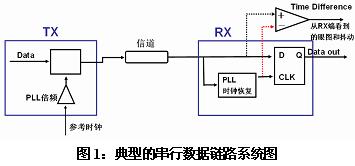

下圖1所示為某串行數據鏈接的系統圖,在Fibre Channel、Gigabit Ethernet、SDH等串行鏈路中都采用了這樣的架構。發送端(TX)發送的信號通過信道傳輸到接收端(RX)后,收發器芯片RX部分的時鐘恢復電路從串行數據中恢復出時鐘,用恢復的時鐘來同步串行數據,進行采樣。由于多種原因,進入RX的串行數據信號可能有較大的抖動,理想情況下(鎖相環PLL的環路帶寬無窮大時),時鐘恢復電路的PLL輸出的時鐘和RX的輸入數據信號同相,即零抖動,這時,RX的判別電路(如圖1中的D觸發器)有最大的建立時間和保持時間余量。但是,由于PLL的環路響應為低通濾波器特性,只能消除串行數據中低頻段的抖動,不能處理高頻抖動,所以,現實情況中收發器芯片RX端“看到”的眼圖是有抖動的。

在圖1中,RX端PLL的參數是影響眼圖和抖動性能的決定因素。PLL是一種廣泛使用的電子電路,可以用于獲得特定頻率的時鐘、射頻信號調制與解調和串行數據的時鐘恢復。

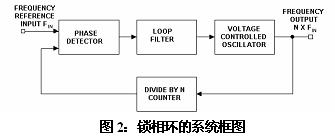

如圖2為PLL的系統圖,包括鑒相器(phase detector)、環路濾波器(loop filter)、壓控振蕩器(voltage controlled oscillator,簡稱VCO)三個基本部分。PLL的工作原理請參考模擬電路書籍。

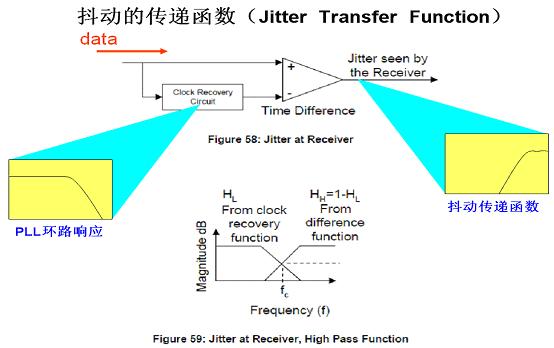

在接收端的PLL中,鑒相器、環路濾波器和VCO三部分組成的環路的頻響為低通濾波器特性。如下圖3所示,接收端的時鐘恢復電路的頻響是一個低通濾波器,其傳遞函數為HL,當串行數據信號的抖動變化頻率較低時,即從直流到PLL的截至頻率,PLL能及時追蹤到數據跳變沿(即鎖住相位),輸出的時鐘與輸入數據同相(嚴格講相位差為固定常數),這樣抖動為零。當連續邊沿的抖動變化太快時(即存在高頻抖動時),PLL不能及時追蹤到邊沿的變化,于是輸出的時鐘和數據邊沿存在抖動,所以,接收端的CDR不能濾除高于截至頻率的抖動,它的抖動傳遞函數(Jitter Transfer Function簡稱JTF)的頻響為高通濾波特性,接收端CDR又稱為TIE抖動的高通濾波器。如圖3,抖動傳遞函數HH=1-HL。

圖3:抖動的傳遞函數

在收發器接收端除了采用如圖1所示的PLL來恢復時鐘外,另一種時鐘恢復方法是使用相位內插器(phase interpolator,簡稱PI),在FBDIMM和PCI Express中都使用PI來恢復時鐘,但是使用儀器測試時,可以用PLL來建模。

測試高速串行數據信號的眼圖與抖動的儀器都使用了基于鎖相環的時鐘恢復方法。其中,實時示波器主要使用軟件PLL來恢復參考時鐘,取樣示波器和誤碼率測試儀都使用硬件PLL來恢復時鐘。實時示波器作為最普及和廣泛應用的測試儀器,本文僅介紹實時示波器的軟件CDR和眼圖測試、抖動測試的關系。

評論