FPGA應用在列車閉塞控制系統提高系統集成與穩定性

列車運行控制系統主要是以對列車運行方向,運行間隔和運行速度進行控制,使列車能夠安全運行且提高運行效率,列車運行控制系統地面設備和車站聯鎖設備主要實現聯鎖控制功能,并生成列車控制所需基礎數據,通過車地信息傳輸通道將地面控制信息傳送給列車,經列車運行控制設備進行處理后,生成列車速度控制曲線,監控列車安全,高速運行,列車控制系統以固定閉塞分區為基礎,分為分級速度列車運行控制系統設備,由地面設備及車載設備兩部分組成。地面設備由軌道電路,列車運行控制中心和維護系統三大部分構成。

本文引用地址:http://cqxgywz.com/article/201706/348664.htm

車載部分由雙重結構組成安全型計算機接收地面傳輸的有關信息,計算并生成速度控制曲線,速度控制與列車速度比較,對超速列車實行制動,列車運行控制中心對軌道電路參數計算形成線路參數,前方目標距離,允許行車速度等不同信息,經調制及鋼軌連續傳輸發給列車。維護系統對地面設備實行遠程診斷與監測管理。

列車的開環控制變為閉環控制,實現了以車載設備為主的行車方式,通信信號一體化是現代鐵路重要發展趨勢,故障安全為最重要的技術條件;列控系統通常由地面控制中心或無線閉塞電路地面信號設備,車地傳輸設備和車載速度控制設備組成,用于控制列車運行速度保證行車安全和提高運輸能力的控制系統,列車的車載系統會適時將車載濾波器轉換到正確的頻率范圍上從而實現列車只接收正確的載波的數據幀,相應的濾波器以電路選擇方式實現以準備好對即將進入區段的采用預定8種載頻之一進行調制的安全數據幀接收和譯碼。

閉塞系統由軌旁盒與室內控制組成,軌旁盒是連接電氣與室內設備的中間設備,是軌道電路室外發送接收設備,系統核心是系統運行控制部分;其關鍵部分是放大濾波板,其實是把發生器發來的調制音頻電壓提升到所需要的電平,并通過帶通濾波器送到軌道饋入點,每種頻率都有自己的專用的放大濾波板。

發送濾波器輸入的信息:

FSK信號:由發送板送人,經調制FSK方波信號,發送濾波器輸出的信息:

FSK正弦波信號,經過電橋,送入方向轉換板,此信號是已經放大和濾去高次諧波的相應頻率的正弦波。

模擬前端硬件

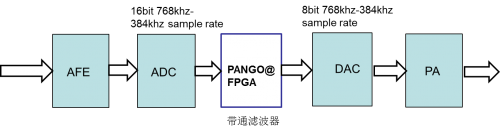

信號接收端由跟隨器,運算放大器以及ADC組成。將接收到的移頻信號進行放大整形送入ADC進行模數轉換,將數字信號送至下級的FPGA實現的高精度FIR濾波器。如圖1-1所示:

圖1-1.FPGA濾波器實現方法

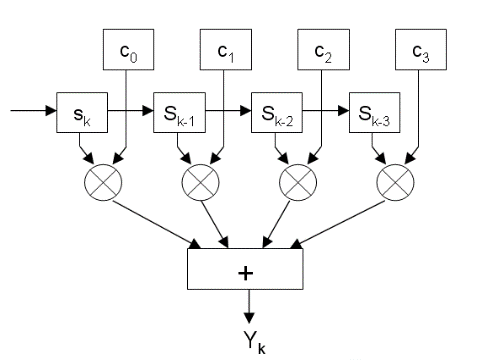

由于帶通濾波器的指標比較高,若要實現相應的指標對于FIR濾波器的階數要求較高需要200階以上,如果采用傳統的濾波器實現方法,則需要耗費大量的邏輯資源和MAC乘累加單元,DFF寄存器需要幾K左右。如圖1-2所示,每一階則需要14bit的DFF資源乘上相應的階數會占用很大的邏輯資源,MAC也需要與階數相同,硬件是無法滿足的。

圖1-2.傳統濾波器實現方法

考慮到同創國芯芯片中已有的資源包括DRM嵌入式存儲器、APM MAC乘累加單元和CLM邏輯單元,以及芯片的性能。采用如圖1-1的實現方法,則可以節省大量的邏輯單元和MAC乘累加器。

通過FPGA實現DSP算法可以極大提高系統性能和降低設計復雜度,以數字FIR 為例,通過優化設計DSP執行乘-累加MAC操作,順序執行N個MAC中每一個操作,因此可達到最大運行速度大約為Fclock/NHz,其中Fclock為DSP最高時鐘頻率,而使用FPGA可以全并行地實現濾波器,其中并行執行N個MAC操作(而不是順序執行)對于同樣的Fclock濾波器執行速度可以提高N倍。大多數DSP提供32位精度累加器用于保存MAC操作結果,而對于FPGA,理論上可以實現任意精度的操作,可以在10-16位寬度范圍內實現大部分濾波器功能。

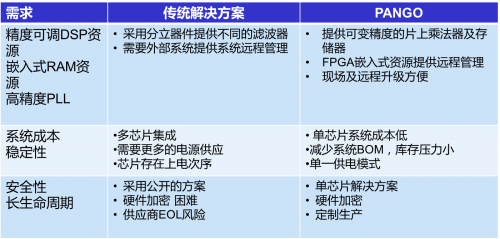

使用FPGA在閉塞列控系統的優勢非常明顯:

同創國芯TITAN@系列可編程邏輯器件采用了完全自主產權的體系結構和主流的40nm工藝。 PG系列產品包含創新的可配置邏輯單元(CLM)、專用存儲單元(DRM)、算術處理單元(APM)、多功能高性能I/O以及豐富的片上時鐘資源等模塊,為客戶提供高性能,大容量,差異化應用的FPGA產品。 我們創新的提出具有自主知識產權的邏輯架構“CLM”(Configurable Logic Module, 可配置邏輯模塊)-- 是TIIAN系列器件的基本邏輯單元,主要是由多功能LUT5,寄存器以及擴展功能選擇器等組成,CLM集成了專用電路實現4:1多路選擇器功能和快速算術進位邏輯;擴展功能選擇器主要用于實現寬位查找表和輸出選擇功能. 這樣客戶在實現同級間邏輯級聯可以得到更高的速度;此外相鄰的兩個CLM之間還有一條基于LUT7的專用級聯鏈,用于組合生成LUT8。CLM的使用可通過關聯的綜合工具(Synplify Pro)和同創國芯電子有限公司的軟件Fabric Compiler來完成。CLM還可通過同創國芯軟件IP Compiler工具來構成分布式RAM IP.舉個例子,在SDH 應用領域為了實現SDH的嚴格同步時序需求,其支路單元TUPP 的管理指針為了適應多路同步數據就需要更多的邏輯資源去同步數據,勢必造成邏輯的大量耗費,而分布式RAM 可以使以上設計節省大量的資源。

使用FPGA 替代傳統分立器件和傳統DSP器件可以精簡系統器件,降低EMI風險及提高設計靈活性,而且設計資源可以重復利用提高設計資源的利用率,為企業降低資金投入。

評論