PowerPC 440 處理器模塊

面積利用率高、性能高的嵌入式系統 創新型 Virtex™-5 FXT 平臺提供了一流的 FPGA,從而提供了2個帶有32位 RISC 核的行業標準 PowerPC® 440 處理器(每個都在它自己的嵌入式外設模塊內)。

簡介

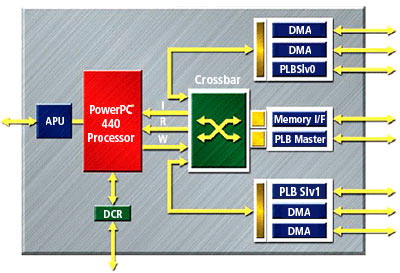

- 1,100 DMIPS @ 550MHz 處理器;利用帶有2個處理器的單個 FPGA 實現了 2,200 DMIPS 的性能

- 新的5 x 2、128位縱橫交換機實現了延遲最小化和點到點連接功能

- 同步存儲器總線和處理器本地總線(PLB)接入實現了吞吐量最大化

- 集成式 DMA 通道、PLB 接口和專用存儲器接口實現了邏輯資源利用最小化

- 輔助處理器單元(APU)控制器讓硬件加速器整合變得很輕松

圖1

PowerPC 440 處理器嵌入式模塊。

本文引用地址:http://cqxgywz.com/article/201706/349531.htm深入探討

整合了高速邏輯和軟件靈活性

- 根據您的要求定制嵌入式系統設計

- 利用內置式 PowerPC 440 處理器模塊設計片上系統功能和實時處理功能

- 利用 MicroBlaze™ 軟處理器在全部 Virtex-5 FPGA 內有效地實現控制功能

實現最高吞吐量

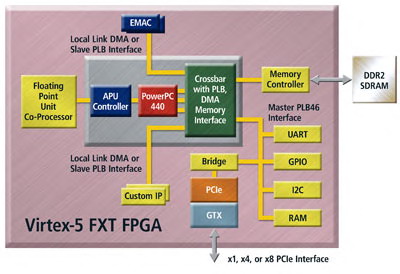

- 獲取到 TEMAC、PCIe 模塊和 FPGA 邏輯的、無阻塞流水線點到點訪問入口

- 利用每周期最高可以傳輸128位數據的專用存儲器接口端口卸載 PLB

- 利用高度流水線化的發射和接收分散集中 DMA 通道實現數據傳輸速率的最大化

- 通過用戶可選的端口優先化和工作頻率來優化系統性能

提升系統性能

- 卸載 CPU 密集型操作,如視頻處理、3D 數據處理和浮點數學運算

- 利用 APU 控制器在 FPGA 邏輯內創建定制協處理器

- 優化硬件/軟件分區,從而實現 FPGA 利用率的最大化和硬件成本的最小化

- 利用 IEEE 754 兼容浮點單元選項實現雙/單精度算術運算

簡化嵌入式開發,推進創新

- 利用獲獎的 Platform Studio 工具套件加快處理設計

- 利用設計向導、可定制 IP 和集成式 HW/SW 套件提高生產率

- 利用 Eclipse SDK 和 ChipScope™ Pro 集成式總線分析器簡化系統級調試

- 行業領導廠商提供的大量的在實時 O/S、設計、調試和跟蹤技術方面的ecosystem 支持

- 利用快速啟動在嵌入式設計的最關鍵的項目階段為您的隊伍提供專家級建議和培訓

圖2

PowerPC 440 處理器系統設計實例。

評論