FPGA實戰開發技巧(11)

5.5.4 從串配置模式

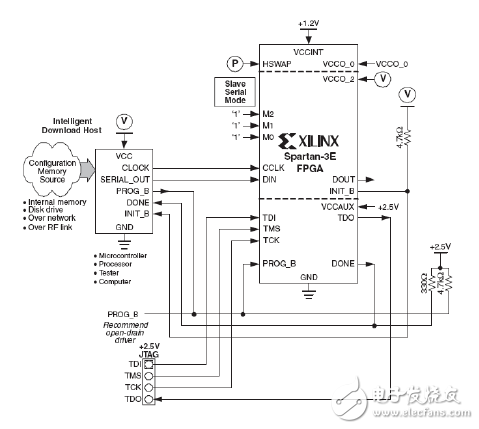

在串行模式下,需要微處理器或微控制器等外部主機通過同步串行接口將配置數據串行寫入FPGA芯片,其模式選擇信號M[2:0]=3’b111。典型的Spartan 3E系列FPGA單片配置電路如圖5.5.11所示。DIN輸入管腳的串行配置數據需要在外部時鐘CCLK 信號前有足夠的建立時間。其中單片FPGA 芯片構成了完整的JTAG鏈,僅用來測試芯片狀態,以及支持JTAG 在線調試模式,與從串配置模式沒有關系。外部主機通過下拉PROG_B啟動配置并檢測INIT_B 電平,當INIT_B 為高時,表明FPGA 做好準備,開始接收數據。此時,主機開始提供數據和時鐘信號直到FPGA 配置完畢且DONE 管腳為高,或者INIT_B 變低表明發生配置錯誤才停止。整個過程需要比配置文件大小更多的時鐘周期,這是由于部分時鐘用于時序建立,特別當FPGA 被配置為等待DCM鎖存其時鐘輸入。

本文引用地址:http://cqxgywz.com/article/201710/365626.htm

圖5-32 FPGA從串配置電路示意圖

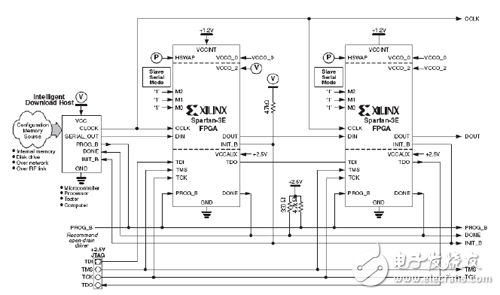

此外,從串配置模式也可配置多片FPGA芯片,典型的兩片Spartan 3E系列FPGA的從串配置電路如圖5-33所示。所有芯片的CCLK信號都有主控設備提供,靠近主控設備的FPGA要充當橋梁的作用,將配置數據轉發到第二個FPGA芯片。可以看到采用從串配置的好處主要在于節省電路板面積,并使得系統具備更大的靈活性。

圖5-33 多片FPGA從串模式配置電路

5.5.5 JTAG配置模式

1.JTAG配置電路

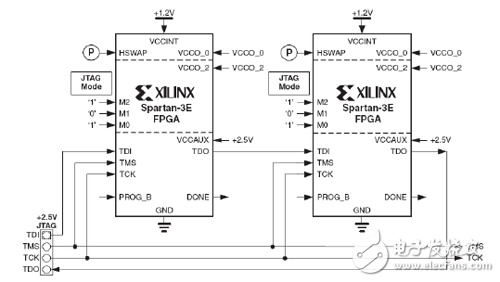

賽靈思公司的FPGA芯片具有IEEE 1149.1/1532協議所規定的JTAG接口,只要FPGA上電,不論模式選擇管腳M[2:0] 的電平,都可用采用該配置模式。但是將模式配置管腳設置為JTAG模式,即M[2:0]=3’b101時,FPGA芯片上電后或者PROG_B管腳有低脈沖出現后,只能通過JTAG模式配置。JTAG模式不需要額外的掉電非易失存儲器,因此通過其配置的比特文件在FPGA斷電后即丟失,每次上電后都需要重新配置。由于JTAG模式已更改,配置效率高,是項目研發階段必不可少的配置模式。典型的Spartan 3E系列芯片的JTAG配置電路如圖5-34所示。

圖5-34 JTAG模式配置電路示意圖

5.5.6 System ACE配置方案

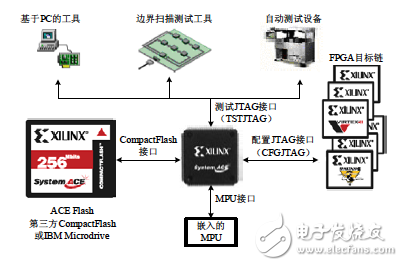

隨著FPGA成為系統級解決方案的核心,大型、復雜設備常需要多片大規模的FPGA。如果使用PROM進行配置,需要很大的PCB面積和高昂的成本,因此很多情況下都利用微處理由從模式配置FPGA芯片,但該配置方案容易出現總線競爭且延長了系統啟動時間。為了解決大規模FPGA的配置問題,賽靈思公司推出了系統級的System ACE(Advanced ConfiguraTIon Environment) 解決方案。

System ACE可在一個系統內,甚至在多個板上,對賽靈思的所有FPGA進行配置,使用Flash存儲卡或微硬盤保存配置數據,通過System ACE控制器把數據配置到FPGA中。目前,System ACE有System ACE

CF(Compact Flash)、System ACE SC(Soft Controller) 以及System ACE MPM(MuTI-Package Module) 三種。讀者需要注意的是:System ACE SC/MPM 是和System ACE CF 獨立的解決方案。典型的ACE 接口以及系統組成如圖5-35 所示。

圖5-35 典型的ACE接口以及系統組成示意圖

1.System ACE CF解決方案

System ACE CF的核心是System ACE CF存儲設備和System ACE控制器芯片。System ACE CF存儲設備包括賽靈思的ACE Flash卡或其它廠家的Compact Flash卡以及IBM的微硬盤。Compact Flash卡的容量為32MB~4GB,微硬盤的容量為2GB~6GB,至少可配置數百片FPGA芯片。

System ACE CF控制器提供了存儲單元和FPGA器件之間的接口,PC和存儲器的標準JTAG接口。控制器芯片默認的配置模式也是通過邊界掃描的方式將數據配置到FPGA 鏈中,同樣可由邊界掃描鏈的測試和編程接口來輔助進行系統原形的調試,其主要特點有:

- 支持賽靈思所有FPGA芯片的配置;

- 以最小的PC板空間實現多達8Gb的配置 ;

- 包括高達152Mbps的配置速率;

- 利用帶有嵌入式處理器核的FPGA進行系統調節;

- 管理多個比特流( 全部或部分),并按需要對其進行激活;

- 包含處理器核初始化;

- 軟件存儲加密;

- 可移動存儲器件;

- 降低了定制配置系統的成本,支持大多數 CompactFlash卡,包括Microdrive單元;包含內置式微處理器接口,可以直接調整FPGA配置;釋放設計資源。

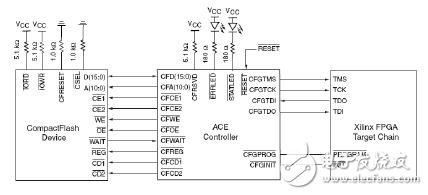

圖5-36 System ACE CF配置電路示意圖

Compact Flash接口是ACE控制器的關鍵接口,可連接Compact Flash卡、標準的Compact Flash模塊以及IBM微硬盤。Compact Flash可以進行拆卸,因此對存儲內容進行修改和升級以及更換容量都非常方便。Compact Flash接口由Compact Flash控制器和Compact Flash仲裁器兩部分組成。由System ACE CF配置FPGA的接口電路如圖5-36所示。

2.System ACE SC解決方案

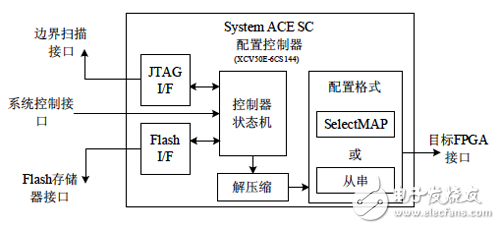

System ACE SC為用戶提供了自主性,用戶可以自由地選擇每一部分的元件,可將其置于電路板的任何位置,且所有的功能在一個獨立的FPGA中完成,并不需要整合其他組件。System ACE SC有4個主要接口:邊界掃描JTAG接口、系統控制接口、Flash存儲器接口以及FPGA 接口,如圖5-37所示。

圖5-37 System ACE SC接口示意圖

其中JTAG接口主要提供邊界掃描測試和對具有JTAG接口的Flash存儲器通信;Flash接口主要和外邊的Flash芯片通信,讀取存儲器內的內容以及對存儲器進行編程;系統控制接口主要提供輸入時鐘、配置控制信號和配置狀態信號等;FPGA 接口主要用于配置FPGA,可通過從串、從并以及Selec tMAP等配置模式。

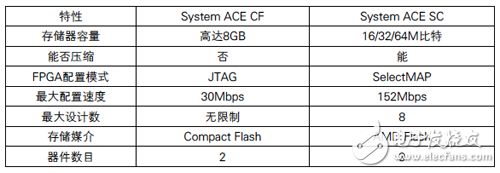

System ACE SC和System ACE CF的主要區別在于,System ACE SC的控制器是一個軟核邏輯,而不是芯片,需要和設計一起下載到FPFA中。其余區別如表5-4所列。

表5-4 System ACE CF和System ACE SC的區別

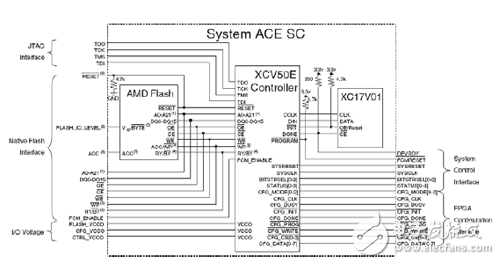

典型的System ACE SC 配置電路如圖5-38 所示。

圖5-38 System ACE SC配置電路示意圖

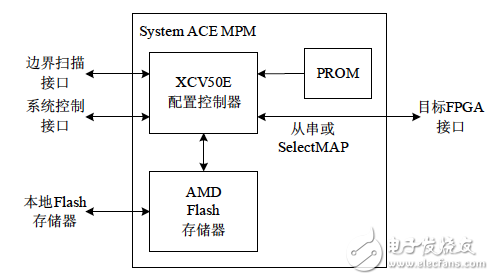

3.System ACE MPM解決方案

System ACE MPM是一個整合的組件解決方案,包括FPGA和PROM組成的配置控制組件和一個Flash存儲組件,并封裝為一個模塊,通過盡可能少的組件來實現配置電路。賽靈思公司有16M、32M 以及64M位低密度的System ACE MPM。System ACE MPM 有4 個主要接口,和System ACE SC 的接口一樣,其特征和功能也與System ACE SC 一樣。二者的區別在于:System ACE MPM 封裝了整個配置模塊,而System ACE SC 允許用戶自行配置,其接口電路如圖5-39 所示。

圖5-39 System ACE MPM接口電路示意圖

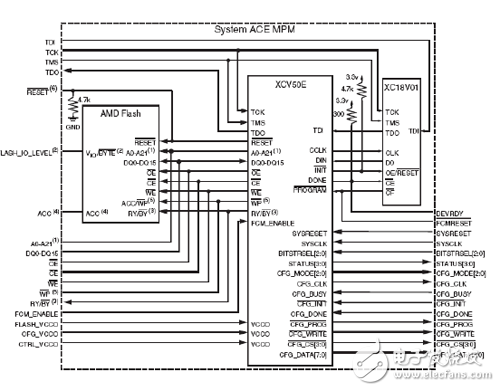

System ACE MPM是賽靈思公司第一個支持位流壓縮的配置方案,支持多種配置模式,同時可多達8個FPGA鏈的從串配置模式和多達4個FPGA的Select MAP配置模式,最大配置速率為152Mbps,同時又可最大限度地減小電路板空間和連線。典型的System ACE MPM 配置電路如圖5-40所示。總之,System ACE技術簡化了大型FPGA 系統的配置方案,令開發人員將精力主要集中在系統性能的提高和開發時間的縮短。

圖5-40 System ACE MPM配置電路示意圖

評論