工程師設計經驗分享:畫FPGA開發板所犯的那些錯誤

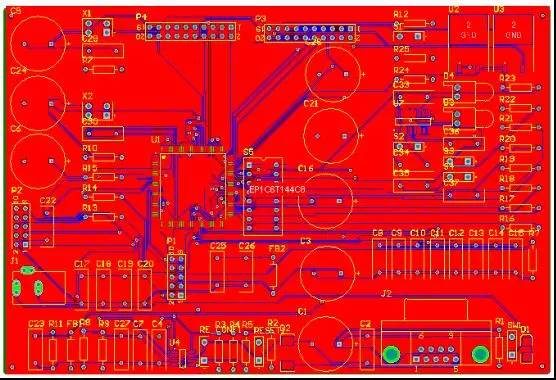

畫FPGA開發板所犯的那些錯誤,小編這里先截下我最初畫這個開發板的一張“慘不忍睹”的PCB讓大家看看。

本文引用地址:http://cqxgywz.com/article/201805/379374.htmTop Layer如圖:

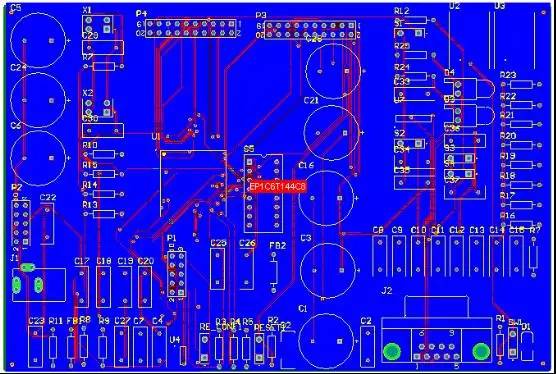

Bottom Layer如圖:

第一遍畫的時候,想“速戰速決”把它畫完,草草了事,但是等全部布線完以后卻發現這里面的錯誤實在是太多了,我覺得最核心的錯誤就是一開始就沒有注意整個系統各個元器件的布局,從而導致了“災難”的發生,后來的布線也就非常困難。大家很容易可以在上圖中看出布線的長度大部分都很長,其實這也是非常嚴重的錯誤,尤其對于高速信號線來說。輸入、輸出端用的導線應該盡量短,且盡量不要長距離的平行,當然,差分線除外。我們知道,其實每個元器件都會有引腳電感,從芯片的引腳導線到電阻、電容和電感線圈的引線,每條線和走線都有寄生電容和電感,它們直接影響著導線的阻抗并且對高頻率敏感。

一般來說,在低頻段時導線主要呈現電阻特性,而根據RF電路理論可知,在高頻段時,導線會呈現電感特性,我畫的這個板子是25MHz的,所以可以對這個因素含糊一點了,但是,為了防止帶來不必要的麻煩,在走高頻信號線時還是小于150MHz波長的1/20為好,以免在板子上形成意外的干擾源,因為當信號頻率達到150MHz以上時,PCB走線就相當于“變成”了一個有效的天線了!

我們還得注意一下差分信號的走線,很重要的一點就是差分信號線在板子上的走線必須一樣長,而且對于信號速率在一百MHz以上的,還得選用帶阻抗控制的高速連接器,我畫這塊板子的時候不需要考慮這點,但我還是提防了一下,順便在這里提一下,嘿嘿,要是以后遇到這么高的頻率時,就得好好斟酌了,否則會引發EMI問題喔。

不知道大家有沒有發現,在上面我畫的PCB中其實蘊含著一個很好的優點,那就是整個板子的過孔很少!大家應該都知道,在布線時,我們應該盡量少用或者不用過孔,因為這個會帶來更多的集總線模型電感,這就可能會使信號質量降低,更有甚者會引發EMI問題,那可就比較麻煩了。

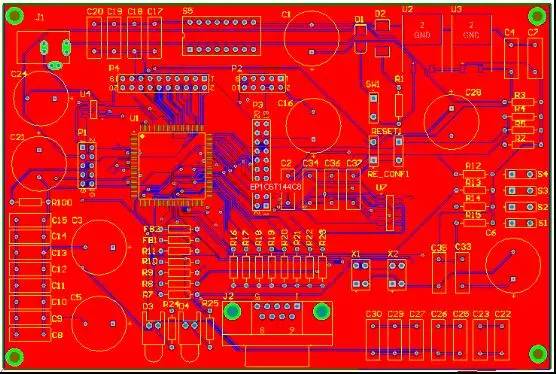

之后我又重新好好地畫了幾次,再截個圖看看,

Top Layer如圖:

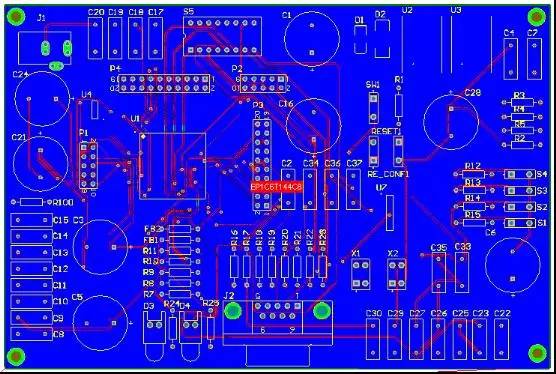

Bottom Layer如圖:

感覺比第一遍畫的圖還是有改進的,但肯定還可以畫得更好,只是覺得目前的話,就這個水平了,以后再慢慢練!

評論