基本ESD模型及功能參數

將一個電容充電到高電壓(一般是2kV至8kV),然后通過閉合開關將電荷釋放進準備承受ESD沖擊的“受損”器件(圖1)。電荷的極性可以是正也可以是負,因此必須同時處理好正負ESD兩種情況。

本文引用地址:http://cqxgywz.com/article/202210/438851.htm(1)HBM(Human Body Model),人體放電模型;

指帶電荷的人體與集成電路產品的管腳接觸并發生靜電荷轉移時,產生的ESD現象。

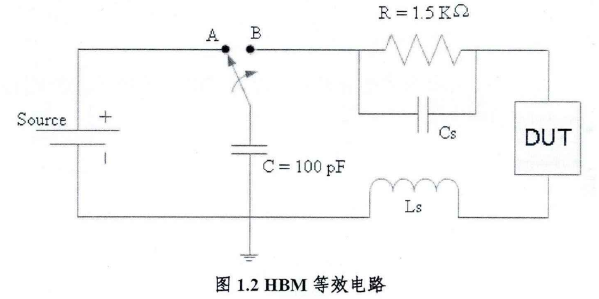

人體等效電阻約1500歐姆,等效電容值為lOOpF,Ls與Cs寄生電感和電容。該ESD放電產生電流波形的上升時間在2~10ns范圍內,持續時間在150~200ns范圍內.由于HBM模型中的電感、電容等參數針對于不同環境和人體會有所差異,因此各組織機構制定各自HBM模型中的寄生電容、電感值略有差異,但其HBM放電波形基本一致。

(2)MM(Machine Model),機器放電模型;

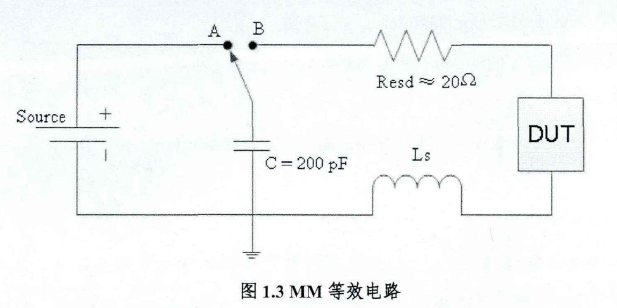

模擬機器手臂等金屬工具與芯片管腳接觸并發生靜電荷轉移,產生的ESD事件。

金屬機械的寄生電阻較小(約20歐姆)、等效電容較大(200pF)且存在寄生電感Ls,因此MM放電過程維持時間短,電流波形呈阻尼振蕩且峰值電流較高,一般為相同等級HBM ESD峰值電流的20~30倍。MM波形上升時間在6~8ns范圍內,脈寬約為100ns。

備注:MM模型,由于電阻過小,實驗嚴苛,目前已經基本不再進行,用CDM代替;

(3)CDM(Charged Device Model),組件充電模型;

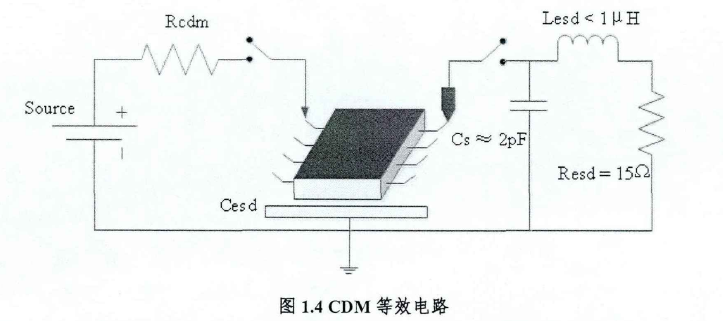

主要模擬封裝后的芯片在裝配、運輸中由于摩擦或者感應自身攜帶了電荷,當芯片管腳接觸到地或其他物體引起電荷轉移,大量電荷從IC內部流出產生的ESD現象。

芯片本身的寄生電阻、電容和電感與芯片的版圖尺寸、封裝形式、放電位置等都有密切關系。芯片寄生電阻較小(約15歐姆),因此CDM放電過程迅速,其電流波形的上升時間約為0.2ns~0.4ns,脈寬小于5ns,電流峰值也較大,約為相同等級HBM ESD的15~20倍。由于其電流脈沖上升時間極短,對ESD防護器件的開啟速度要求十分嚴格。

(4)HMM(Human-Metal-Model),人體金屬放電模式;

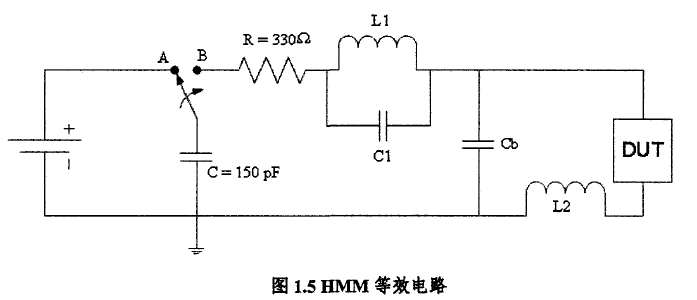

業界最新研究的一種ESD模式,主要模擬帶有靜電荷的人體通過金屬、機械等與芯片管腳相接觸,發生電荷轉移的ESD過程。

HMM主要用來評價芯片在系統級ESD測試中的魯棒性。該模型尚在廣泛討論當中,并無標準的模型和參數,只有兩個指導性文檔ESD TR5.6-01-09和DSP5.6。

備注:上圖中模擬了一種人體金屬模式等效電路圖,等效電容為150pF,等效電阻約為330^2,L1、C1、L2為放電回路寄生參數,Cb為平板電容,其放電波形的上升時間大概為0.8ns±0.2ns,持續時間約為50ns。

ESD失效原因

失效類型分為兩大類:致命失效&性能退化;

致命失效:介質擊穿、金屬溶斷、PN結穿刺、接觸孔金屬電遷移等,它會直接造成開路、短路或漏電增大,導致芯片永久性失效;

性能退化:會造成芯片內部電路參數漂移、壽命降低,影響芯片的工作性能但一般不會立刻導致芯片失效。

ESD保護電路的功能

其在芯片功能正常工作時處于透明狀態,不影響產品性能參數,占據芯片版圖面積小,并且在ESD應力下能夠及時快速的開啟,將ESD電流通過ESD防護電路順利泄放,將芯片內電壓箱位在安全范圍,有效保護芯片內部胞弱的晶體管,同時ESD防護器件本身要足夠強壯而不被ESD應力損壞。這就要求了設計優異ESD防護器件應滿足的四個標準:透明性、敏捷性、有效性和魯棒性。

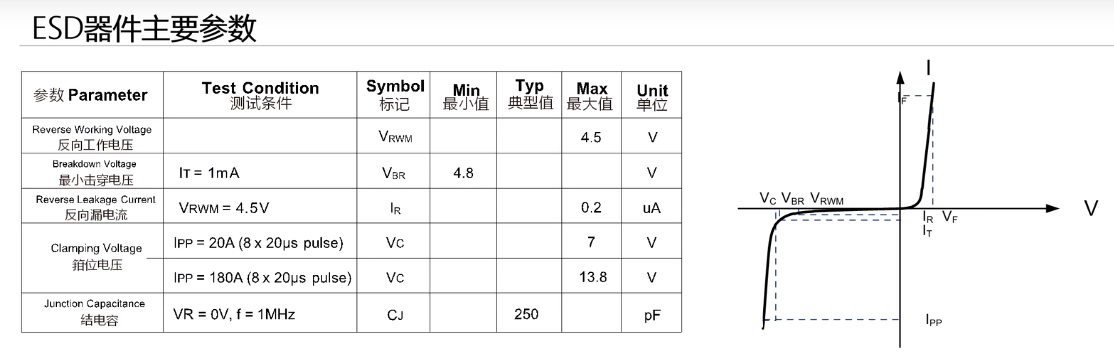

ESD關鍵參數

說明:

反向工作電壓:對應線路上的工作電壓or最高變頻電壓;

最小擊穿電壓:測量方式為反向電流1mA時的電壓;

反向漏電流:在最大反向工作電壓對應的電流;高阻端口

鉗位電壓:當電路經過8個20us的pulse后,在規定電流下的殘余電壓;為了確保在8個20us的pulse后,電路依然可以正常工作;

結電容:速率高的場景,對結電容敏感;

注意:

ESD的截止電壓需要大于被保護IC的最大工作電壓,否則會影響電路正常工作;如:工作電壓為5V的線路,應選擇截止電壓大于等于5V的ESD器件進行保護;

在高速端口(如:USB 3.0,USB3.1,HDMI,IEEE1394等),ESD保護器件的結電容應選擇盡量小,以避免影響通信質量;

根據電路設計布局及被保護線路選擇合適的封裝形式。一般情況下:ESD器件封裝大小從一定程度上可以反應防護等級大小,一般封裝越大,可容納的ESD芯片面積也越大,防護等級也越高;

接口盡量靠近大面積的底線,泄放回路也是越短越好;

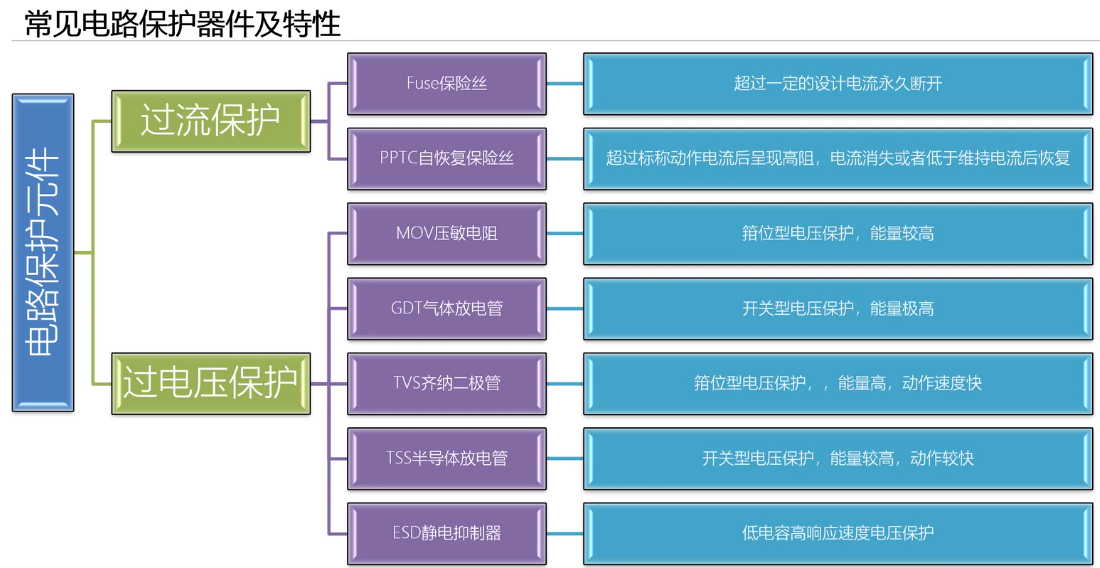

電路保護器件

————————————————

版權聲明:本文為CSDN博主「這么神奇」的原創文章,遵循CC 4.0 BY-SA版權協議,轉載請附上原文出處鏈接及本聲明。

原文鏈接:https://blog.csdn.net/weixin_47139649/article/details/118991612

評論