基于USB和FPGA的隨機數發生器驗證平臺

摘要:為了方便基于FPGA實現的隨機數發生器的驗證與演示,以CycloneII FPGA芯片EP2C20Q240C8N為核心,設計實現了隨機數發生器IP核下載與測試的開發驗證平臺,并詳細闡述了各模塊的設計原理及關鍵技術。最后,通過下載運行隨機數生成系統,對整個平臺功能進行了檢驗。結果表明,各模塊電路工作正常,平臺性能穩定。

關鍵詞:FPGA;隨機數發生器;驗證平臺

引言

隨機數發生器是信息安全領域不可或缺的重要組成部分,廣泛應用于金融、軍事等信息安全保密通信的電子設備中。目前,隨著對RNG體積、功耗、接口方式等要求的提高,設計集成化芯片或IP核形式的隨機數發生器成為一種必然。為此,基于純數字電路實現的隨機數發生器已成為研究的熱點,而FPGA可編程邏輯芯片為此類隨機數發生器的研究提供了良好的開發環境。

為方便隨機數發生器IP核的下載、運行及測試,同時保證產生的隨機數能夠快速地傳送給主機進行隨機性檢測,本文以FPGA芯片為核心,以USB接口為通信接口,設計實現了一個隨機數發生器的驗證平臺。該平臺結構簡單,功能完善,對于其他特殊應用的驗證平臺搭建也具有指導意義。

1 系統硬件結構及工作原理

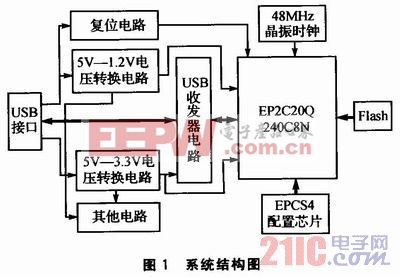

隨機數發生器驗證平臺主要由CycloneII FPGA芯片EP2C20Q240C8N、與主機進行通信的USB收發器電路、下載配置芯片EPCS4、頻率為48 MHz的時鐘源芯片、外部存儲器(Flash)、兩個電壓轉換電路、復位電路和其他電路組成,如圖1所示。

在每次實驗演示時,將該芯片通過USB口與PC機相連,由主機為平臺提供5 V電源,當與主機連通后系統上電,復位電路進行工作,對整個系統進行復位。以QuartusII 7.2為開發環境,采用ByterBlsterII下載電纜,通過JTAG下載口或以AS下載方式,通過配置芯片EPCS4將隨機數發生器系統下載到實驗平臺中,最終通過USB口連接主機與平臺進行信息交互。由主機向系統發送命令,在系統控制下,產生的隨機數通過USB收發器傳送給主機,主機接收數據后進行隨機性的各項檢測。

2 核心器件和關鍵技術

2.1 FPGA芯片EP2C20Q240C8N

EP2C20Q240C8N芯片是A1tera CyeloneII系列產品中的一員,它采用TSMC1.2 V、90 nm和低電介絕緣工藝技術,由12英寸(300 mm)晶圓制成,具有潛在速度方面的極大優勢。

評論