如何確定數字控制系統的ADC/DAC性能

轉向數字控制器

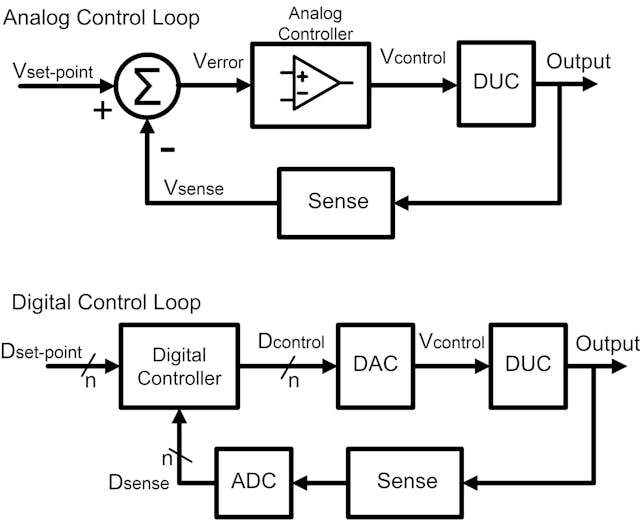

雖然許多集成電路仍然在特定應用中使用模擬反饋,例如偏置控制、電壓調節、鎖相環 (PLL) 或自動增益控制 (AGC),但通用嵌入式和工業控制器已過渡到數字實現,以獲得更大的靈活性和集成度。模擬系統的數字仿真的概念意味著數字系統必須充分再現模擬功能,ADC 和 DAC 構成數字控制器和現實世界之間的關鍵接口。

在實際的行業環境中,大多數數字控制器不是嚴格依賴經典的控制理論數學,而是采用比例積分微分 (PID) 元素,其調整通常是根據經驗進行的。MCU 和 PLC 通常可以在內部處理完整的數字 PID 實現,使其具有成本效益、高效,并且可以通過軟件參數更改輕松調整。

在數字控制設計中必須考慮幾個關鍵因素:

· 系統所需的 DUC 輸出精度

· 需要DAC分辨率、時鐘速率和紋波性能

· 傳感器精度、ADC 分辨率和采樣率

· 數字數學精度

雖然第一對考慮因素適用于模擬和數字系統,但ADC和DAC的具體性能在數字實現中尤為重要。傳感器精度應超過所需的 DUC 輸出精度,并且控制算法的計算精度應超過 DAC 性能,以避免引入新的誤差。

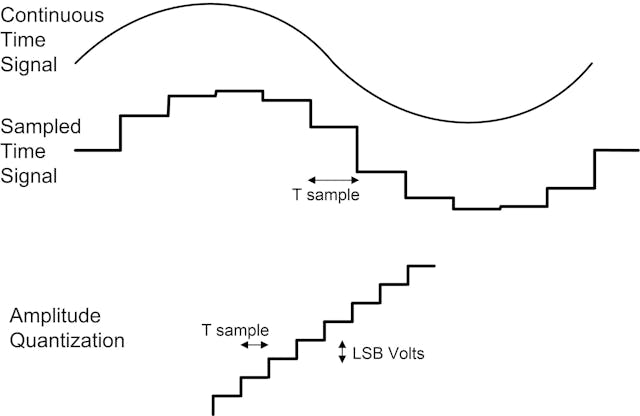

連續時間DUC信號(圖2)由ADC及時采樣并量化幅度,從而生成輸入到數字控制器的數字數據流。因此,ADC的采樣率和分辨率將限制檢測和控制DUC的精度。估計適當的ADC采樣率通常涉及檢查DUC的時域階躍響應——ADC的幅度分辨率越精細,單位時間內的樣本越多,數字系統可實現的控制就越精細。

DUC 測試設置

DUC 的穩定性是控制系統設計中的一個關鍵屬性。反饋控制環路提高了 DUC 的穩定性,但僅限于其帶寬內。DUC 中超過控制系統帶寬的高頻變化仍未得到補償。

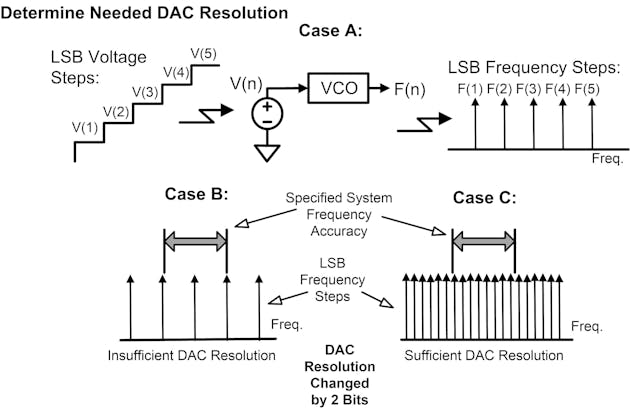

圖 3 說明了在沒有干擾(例如負載或溫度變化)的穩定環境中,固定輸入應產生固定 DUC 輸出的測試設置。一個例子是壓控振蕩器 (VCO)。即使具有穩定的模擬輸入,固有相位噪聲和頻率抖動也會導致輸出頻率變化。

DUC 的直流傳遞函數是輸入(例如電壓)和輸出(例如頻率)之間的關系,決定了所需的 DAC 分辨率(圖 4)。通過將系統所需的最小-最大輸出精度映射到相應的最小-最大DAC輸入值,可以定義DAC所需的最小步長(最低有效位或LSB)。為了實現穩健的設計,建議在所需的精度窗口內有八個或更多 DAC LSB 步進。

測試裝置(情況 A)將一系列電壓階躍輸入到 DUC,并測量輸出頻率。輸入應來自低噪聲直流電源,以完全隔離和測試 DUC 性能。如果初始分辨率不足(如情況B所示),則添加額外的DAC位可提高性能,如圖4的情況C所示。

如果多個DAC LSB階躍包含在系統的精度范圍內,則會出現設計裕量,從而保護設計免受小誤差或漂移的影響。但是,如果DAC分辨率不夠,控制系統可能無法在閉環作中達到所需的DUC精度。

如圖5所示,對于固定數字輸入,DAC輸出理想情況下應保持穩定。一些DAC,尤其是那些使用脈寬調制(PWM)的DAC,會產生紋波,如果輸出方差超過DAC的LSB粒度,則LSB分辨率無關緊要。

ADC 的作用

ADC的目的是將DUC的檢測電路輸出數字化,其分辨率、可重復性和精度超過系統的整體精度要求。使用與DAC相同的方法,ADC分辨率設置為比所需的DUC輸出分辨率更精細。

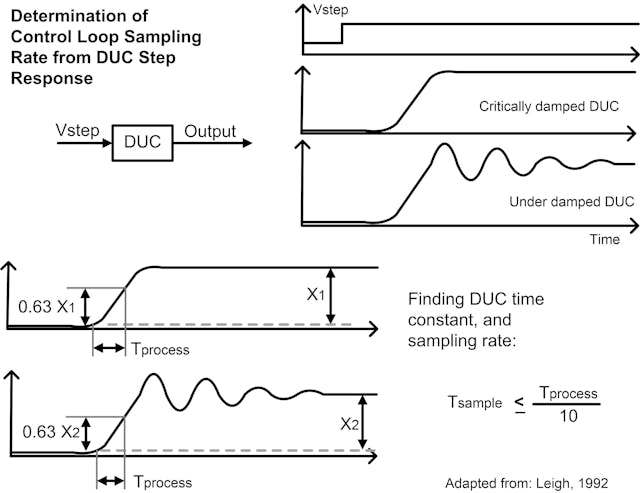

確定ADC的采樣率需要仔細注意。雖然控制工程教科書可以將ADC采樣率與控制環路的帶寬聯系起來,但在實踐中,參考DUC的階躍響應是有效的(圖6)。

開環階躍響應反映了 DUC 對突然輸入變化的反應,揭示了關鍵時間常數(過程時間、T過程)。設置采樣周期(T樣品)以在 T過程中收集至少 10 個樣品是一個實用的指導方針。這確保了控制器準確感知系統動態并能夠做出適當的反應。

在 DUC 的中點工作范圍內應用階躍輸入可確保有意義的表征。例如,對于0至1V DUC輸入,施加從450 mV到550 mV的階躍可以避免極端情況下的非線性。

一旦確定了ADC的最小位深度和采樣率,就可以選擇合適的轉換器,以達到與計算要求相同或更好的性能。然后,所選ADC的最大采樣率定義了環路的工作速率。然后可以選擇具有匹配或更好分辨率和速度的相應DAC來支持輸出側。

這些方法允許設計人員在數字控制環路中指定ADC和DAC性能,支持各種可能的控制算法——從PID到更復雜或定制的方法。有關嵌入式應用的控制理論、調諧、傳感器接口和硬件電路的更多詳細信息,請參閱有關應用嵌入式電子學的綜合文本,包括作者的書《應用嵌入式電子學 – 魯棒系統的設計要點》。

(注:本文來源于《EEPW》202508期)

評論